# 125mW免输出耦合电容的立体声线路驱动器/耳机放大器

#### ■ 特点

- ·输出无需隔直流电容

- ·卓越的低音效果

- ・ 无咔嗒/噼噗声

- ·低THD+N: 最低0.002%

- ·低噪声, V<sub>N</sub>:8μV

- · 支持单端输入和全差分输入

- ·1.65V至4.8V较宽的电源工作范围

- ·输出功率: 125mW (f<sub>IN</sub> = 1kHz, V<sub>DD</sub>=4.2V,

$R_L=32\Omega$ , THD+N=0.1%)

·无铅封装, QFN16L-PP 3mm\*3mm

#### ■ 应用

・耳机

・多媒体音频接口

・机顶盒

· 蓝光/DVD播放器

·LCD电视

・音频消费电子产品

#### ■ 概述

HT97180(L)是一款差分输入/单端输入、可直接输出驱动的耳机放大器/线路驱动器。4.2V供电时,器件可为32ohm耳机提供125mW的功率而不失真。器件可通过外部电阻调节增益(固定增益6dB版本需要提前定制)。器件在音频范围内具有卓越的THD+N表现。

器件具有较宽的电源工作范围,最低支持1.6V电源电压供电。

器件的启动时间为4.2ms, 另130ms的版本需要提前定制。

器件内部集成电荷泵产生负电压,器件输出级由输入正电压和 该负电压驱动,使得输出偏置在零电位,省去了大尺寸、容易引入 失真的输出耦合电容。

器件使能开关时,没有咔嗒/噼噗声。

器件封装为3mm x 3mm, 16-pin QFN-PP, 能在 -40°C 至 +85°C 温度范围内工作。

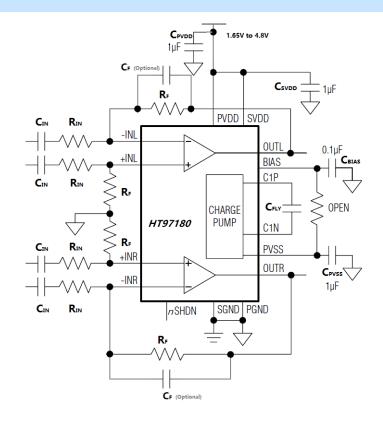

#### ■ 典型应用

# 125mW Direct Drive Line Drivers/Headphone Amplifiers

#### **■** FEATURES

- · Direct Drive Outputs Eliminate DC-Blocking Capacitors, Save Space

- · Excellent Bass Fidelity

- Shutdown and Startup without any Click-Pop Noise

- · Exceptional Low THD+N: 0.002% Minimum

- $\cdot$  Absolutely Low Noise Performance,  $V_N:8\mu V$

- · Differential or Single-Ended Input

- · Wide 1.65V to 4.8V Operating Range

- · Output Power: 125mW (f<sub>IN</sub> = 1kHz,

$V_{DD}$ =4.2V,  $R_L$ =32 $\Omega$ , THD+N=0.1%);

· Pb Free Packages, QFN16L-PP 3mm\*3mm, Extremely Simple BOM Needed

#### APPLICATIONS

- · Headphones · Simple Multimedia Interfaces

- · Set-Top Boxes · Blue-ray and DVD Players

- · LCD Televisions · Prosumer Audio Devices

#### **■** DESCRIPTION

The HT97180(L) is a differential input Direct Drive line driver/headphone amplifier, which can also drive single-ended input signal. It is capable of being driven with 125mW into  $32\Omega$  with a 4.2V supply. The IC is offered with an externally set gain through external resistors (or an internally fixed 6dB gain which needs to be pre-booked. The external gain setting nodes can also be used to configure filters for set-top box applications. The IC has exceptional THD+N over the full audio bandwidth.

Two versions of the IC can be chosen with different turn-on times ( $t_{\rm ON}$ ). The versions for headphone applications feature a  $t_{\rm ON}$  of 4.2ms while the version, intended for set-top-box applications, which needs to be pre-booked, feature a 130ms  $t_{\rm ON}$ . An on-chip charge pump inverts the power-supply input, creating a negative rail. The output stage of the amplifier is powered between the positive input supply and the output of the charge pump. The bipolar supplies bias the output about ground, eliminating the need for large, distortion-introducing output coupling capacitors. The IC shutdowns and startups without click-pop noise.

The IC is available in a 3mm x 3mm, 16-pin QFN-PP and is specified over the extended  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

#### ■ TYPICAL APPLICATION

-2-

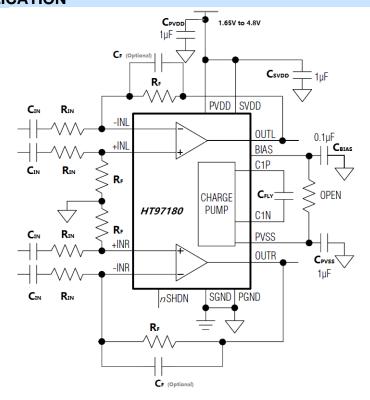

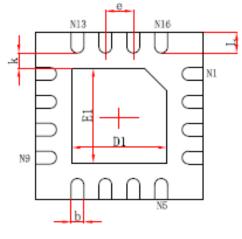

#### **■ TERMINAL CONFIGURATION**

#### **■ TERMINAL FUNCTION**

| PIN | NAME  | Description                                                                        |  |  |  |

|-----|-------|------------------------------------------------------------------------------------|--|--|--|

| 1   | PVDD  | Charge-Pump Power-Supply Input. Bypass to PGND with 1μF.                           |  |  |  |

| 2   | C1P   | Positive Flying Capacitor Connection. Connect a 1µF capacitor between C1P and C1N. |  |  |  |

| 3   | PGND  | Power Ground. Connect PGND and SGND together at the system ground plane.           |  |  |  |

| 4   | C1N   | Negative Flying Capacitor Connection. Connect a 1μF capacitor between C1P and C1N. |  |  |  |

| 5   | PVSS  | Negative Charge-Pump Output. Bypass to PGND with 1μF.                              |  |  |  |

| 6   | SGND  | Signal Ground. Connect PGND and SGND together at the system ground plane.          |  |  |  |

| 7   | INR+  | Right Positive Polarity Input                                                      |  |  |  |

| 8   | INR-  | Right Negative Polarity Input                                                      |  |  |  |

| 9   | SVDD2 | Signal Path Power-Supply Input. Connect directly to PVDD.                          |  |  |  |

| 10  | OUTR  | Right Direct Drive Output                                                          |  |  |  |

| 11  | BIAS  | Internal Supply Node. Bypass to PGND with 0.1µF.                                   |  |  |  |

| 12  | OUTL  | Left Direct Drive Output                                                           |  |  |  |

| 13  | SVDD  | Signal Path Power-Supply Input. Bypass to PGND with 1µF. Connect directly to PVDD. |  |  |  |

| 14  | INL-  | Left Negative Polarity Input                                                       |  |  |  |

| 15  | INL+  | Left Positive Polarity Input                                                       |  |  |  |

| 16  | nSHDN | Active-Low Shutdown. Drive nSHDN high for normal operation.                        |  |  |  |

| _   | EP    | Exposed Pad. Electrically connect to PGND or leave unconnected.                    |  |  |  |

#### ORDERING INFORMATION

| Part Number  | Package Type | Marking              | Operating<br>Temperature Range | MOQ/Shipping Package |

|--------------|--------------|----------------------|--------------------------------|----------------------|

| HT97180SQER  | QFN16L-PP    | HT97180<br>UVWXYZ *1 | -40°C ~ 85°C                   | Tape & Reel 5000PCS  |

| HT97180LSQER | QFN16L-PP    | HT97180<br>UVWXYZ *1 | -40°C ~ 85°C                   | Tape & Reel 5000PCS  |

<sup>\*1</sup> WXYZ/UVWXYZ is production track code.

#### **■ ELECTRICAL CHARACTERISTIC**

#### Absolute Maximum Ratings\*2

| PARAMETER*3                                  | Symbol          | MIN                   | MAX                    | UNIT       |

|----------------------------------------------|-----------------|-----------------------|------------------------|------------|

| Supply Voltage (SVDD, SVDD2, PVDD) Range     | $V_{DD}$        | -0.3                  | +5.5                   | V          |

| PVSS and BIAS Voltage Range                  |                 | -5.5                  | +0.3                   | V          |

| SGND Voltage Range                           | SGND            | -0.3                  | +0.3                   | V          |

| Input (INL+, INL-, INR+, INR-) Voltage Range | V <sub>IN</sub> | -V <sub>SVDD</sub> /2 | +V <sub>SVDD</sub> /2  | V          |

| Input (nSHDN) Voltage Range                  | nSHDN           | -0.3                  | +5.5                   | V          |

| Output (OUTL, OUTR) Voltage Range            | Vout            | -5                    | 5                      | V          |

| C1P Voltage Range                            | C1P             | -0.3                  | V <sub>PVDD</sub> +0.3 | ٧          |

| C1N Voltage Range                            | C1N             | V <sub>PVSS</sub>     | +0.3                   | V          |

| Operating temperature range                  | TA              | -40                   | 85                     | $^{\circ}$ |

| Operating junction temperature range         | TJ              | -40                   | 150                    | $^{\circ}$ |

| Storage temperature range                    | TSTG            | -65                   | 150                    | °C         |

<sup>\*2</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.

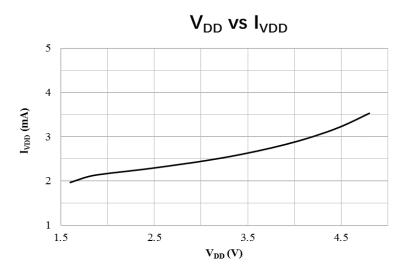

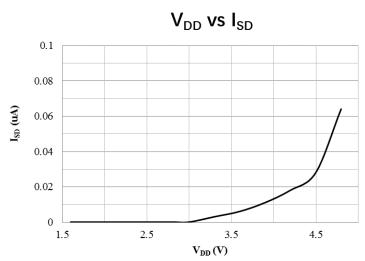

#### Electrical Characteristics\*4

Condition:  $Ta=25^{\circ}C$ ,  $V_{DD}$  (=  $V_{PVDD}$  =  $V_{SVDD2}$ ) = 3.6V,  $V_{PGND}$  =  $V_{SGND}$  = 0V,  $R_{IN}$  =  $R_F$  = 20k $\Omega$ ,  $C_{FLY}$  = 1uF,  $C_{PVDD}$  =  $C_{PVSS}$  = 1uF,  $C_{BIAS}$  = 0.1uF, RL=32R,unless otherwise specified.

| PARAMETER                         | SYMBOL          | CONDITION                            | MIN               | TYP | MAX               | UNIT    |  |

|-----------------------------------|-----------------|--------------------------------------|-------------------|-----|-------------------|---------|--|

| Supply voltage range              | $V_{DD}$        |                                      | 1.65              |     | 4.8               | V       |  |

| Quiescent Supply Current          | I <sub>DD</sub> | No Load                              |                   | 2.7 |                   | mA      |  |

| Under-voltage Lockout             | UVLO            |                                      |                   |     | 1.6               | V       |  |

| Shutdown Supply Current           | I <sub>SD</sub> | nSHDN = 0                            |                   | 0.1 |                   | uA      |  |

| Start-up time                     | ton             | Power on, or pull nSHDN to high      |                   | 4.2 |                   | ms      |  |

| Amplifier                         |                 |                                      |                   |     |                   |         |  |

| Outrot Office Value               | Vos             | HT97180                              |                   |     | 500               | uV      |  |

| Output Offset Voltage             |                 | HT97180L                             |                   | 1   |                   | mV      |  |

| Input Common-Mode                 | M               | Voltage at IN+ and IN-               | -0.5 x            |     | +0.5 x            | V       |  |

| Voltage Range                     | V <sub>СМ</sub> |                                      | $V_{\text{PVDD}}$ |     | $V_{\text{PVDD}}$ |         |  |

| Maximum Differential Input Signal | $V_{DIFF}$      |                                      |                   |     | $V_{\text{PVDD}}$ | $V_{P}$ |  |

|                                   | PSRR            | V <sub>DD</sub> = from 1.65V to 4.8V |                   | 85  |                   |         |  |

| Power-Supply Rejection Ratio      |                 | f <sub>IN</sub> = 217Hz, 200mVpp     |                   | 78  |                   | dB      |  |

|                                   |                 | f <sub>IN</sub> = 10kHz, 200mVpp     |                   | 63  |                   |         |  |

<sup>\*3</sup> All Voltages is referenced to PGND.

# HT97180(L) Headphone Amplifiers

| Common-Mode Rejection Ratio      | CMRR             | $-V_{PVDD}/2 \le V_{CM} \le +V_{PVDD}/2$        |     | 86    |     | dB    |

|----------------------------------|------------------|-------------------------------------------------|-----|-------|-----|-------|

| Output Power                     | Роит             | $VDD = 1.8V$ , $R_L = 32Ω$ , $THD+N = 1%$       |     | 18.5  |     | mW    |

| ·                                |                  | $VDD = 3.3V$ , $R_L = 32Ω$ , $THD+N = 1%$       |     | 80    |     | m\\\/ |

|                                  |                  | $VDD = 4.2V$ , $R_L = 32Ω$ , $THD+N = 1%$       |     | 135   |     | mW    |

|                                  |                  | VDD=1.8V,1kHz, 22Hz to 22kHz BW,                |     | 0.007 |     | %     |

|                                  | THD+N            | $P_{OUT} = 10$ mW, $R_L = 32\Omega$             |     | 0.007 |     | %     |

| Total Harmonic Distortion Plus   |                  | VDD=3.6V,1kHz, 22Hz to 22kHz BW,                |     | 0.005 |     | %     |

| Noise                            |                  | $P_{OUT} = 20$ mW, $R_L = 32\Omega$             |     | 0.003 |     | /0    |

|                                  |                  | VDD=3.6V,1kHz, 22Hz to 22kHz BW,                |     | 0.002 |     | %     |

|                                  |                  | V <sub>ОUТ</sub> = 1.0V, R <sub>L</sub> = 3kohm |     | 0.002 |     | 70    |

| Signal-to-Noise Ratio            | SNR              | P <sub>OUT</sub> = 20mW, 22Hz to 22kHz BW,      |     | 98    |     | dB    |

| Signal to Noise Natio            |                  | A-weighted, R <sub>L</sub> = 32Ω                |     | 30    |     | GD.   |

| Output Noise Voltage             | V <sub>N</sub>   | A-weighted, RIN = RF = $10$ kΩ                  |     | 8     |     | uV    |

| CrossTalk                        | СТ               | $1$ kHz, $P_{OUT} = 20$ mW, $RL = 32$ $\Omega$  |     | -88   |     | dB    |

| CIOSSTAIR                        |                  | 10kHz, $P_{OUT} = 20$ mW, $RL = 32Ω$            |     | -68   |     | ав    |

| Maximum Capacitive Load Drive    | CL               |                                                 |     | 470   |     | pF    |

| External Feedback Resistor Range | $R_{F}$          |                                                 | 4.7 | 20    | 100 | kΩ    |

| Oscillator Frequency             | f <sub>osc</sub> |                                                 | 450 | 500   | 550 | kHz   |

| Logic Input                      |                  |                                                 |     |       |     |       |

| nSHDN Input Logic High           | V <sub>IH</sub>  |                                                 | 1   |       | _   | V     |

| nSHDN Input Logic Low            | V <sub>IL</sub>  | Input Grounded, With or without load            |     |       | 0.4 | V     |

<sup>\*4:</sup> Depending on parts and PCB layout, characteristics may be changed.

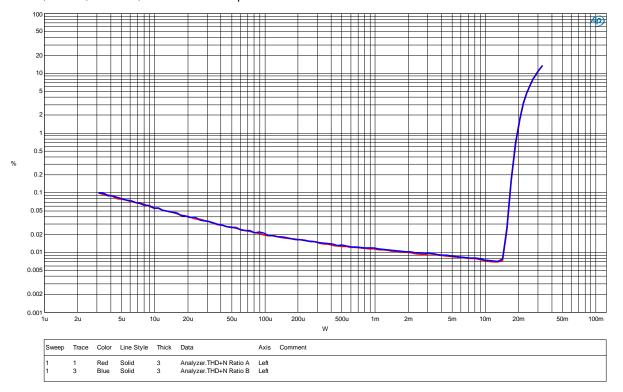

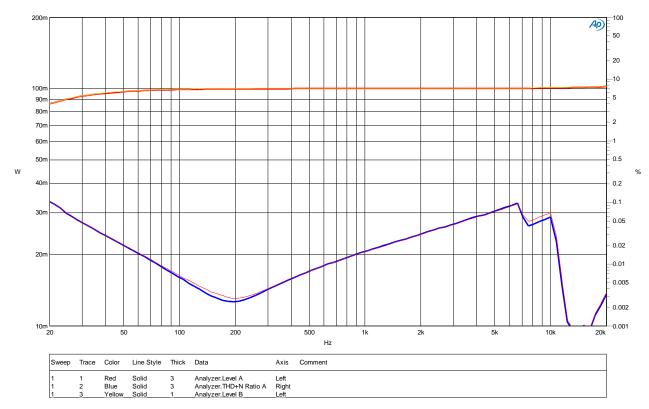

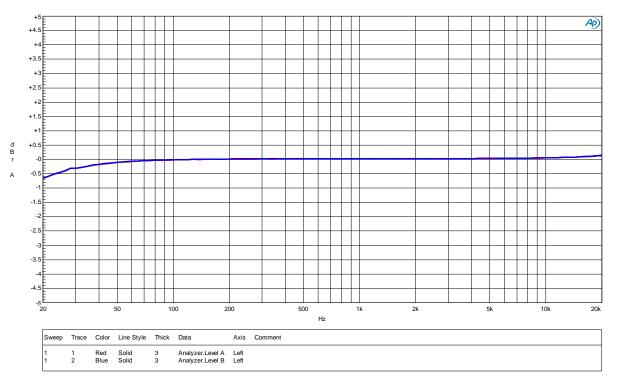

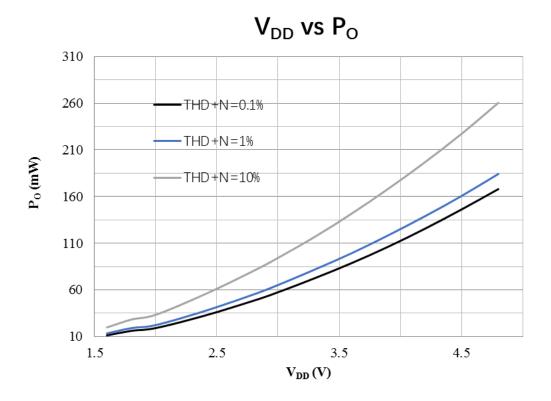

#### **■ TYPICAL OPERATING CHARACTERISTICS**

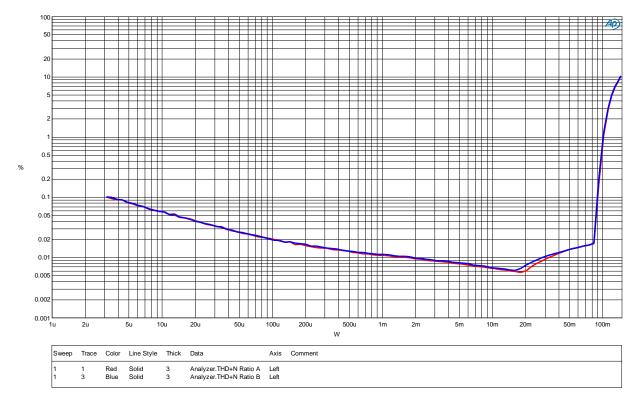

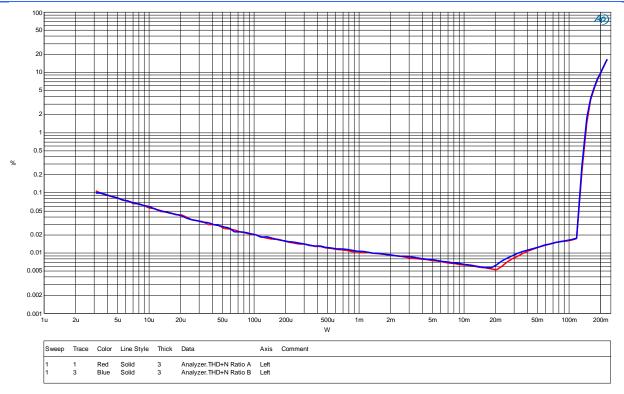

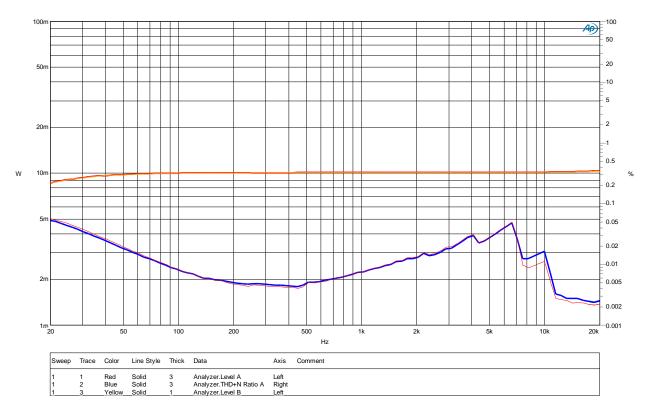

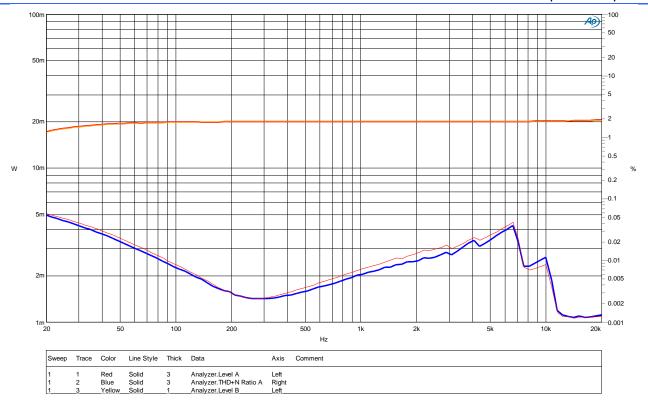

Condition: Ta=25°C,  $V_{DD}$  (=  $V_{PVDD}$  =  $V_{SVDD}$  =  $V_{SVDD2}$ ) = 3.6V,  $V_{PGND}$  =  $V_{SGND}$  = 0V,  $R_{IN}$  =  $R_F$  = 20k $\Omega$ ,  $C_{IN}$  = 1uF, $C_{FLY}$  =  $C_{PVDD}$  =  $C_{PVSS}$  = 1uF,  $C_{BIAS}$  = 0.1uF, $R_{LS}$  = 20k $\Omega$ , fin=1kHz, unless otherwise specified.

Po vs THD+N(VDD=1.8V)

Po vs THD+N(VDD=3.6V)

#### Po vs THD+N(VDD=4.2V)

fin vs THD+N(VDD=1.8V, Po=10mW)

### fin vs THD+N(VDD=3.6V, Po=20mW)

fin vs THD+N(VDD=4.2V, Po=100mW)

Fin vs GAIN

#### ■ APPLICATION INFORMATION

#### 1. Detailed Description

The HT97180(L) is a fully differential input line driver/ headphone amplifier for set-top boxes, LCD TV, and home theater applications where audio fidelity is of primary importance. Power consumption of the amplifier is reduced while maintaining high SNR and THD+N performance. The HT97180(L) require external input and feedback resistors to set amplifier gain. For internal fixed gain of +6dB, it is only available if pre-booked.

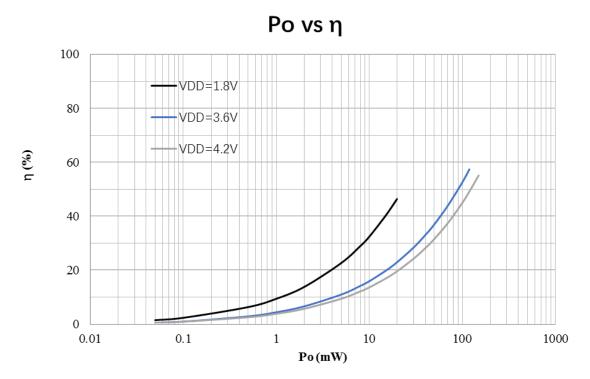

The HT97180(L) operates from a single supply ranging from 1.65V to 4.8V. An on-chip charge pump inverts the positive supply (PVDD), creating an equal magnitude negative supply (PVSS). The headphone amplifiers operate from bipolar supplies with their outputs biased about PGND (Figure 1). The benefit of this PGND bias is that the amplifier outputs do not have a DC component, typically PVDD/2. The large DC-blocking capacitors required with conventional headphone amplifiers are unnecessary, thus conserving board space, reducing system cost, and improving frequency response. Output power of 125mW into  $32\Omega$  is achievable from a 4.2V supply. The device features an under-voltage lockout that prevents operation from an insufficient power supply and click-pop suppression that eliminates audible transients on startup and shutdown.

Fig. 1 Conventional Driver Output Waveform vs. HT97180(L) Output Waveform

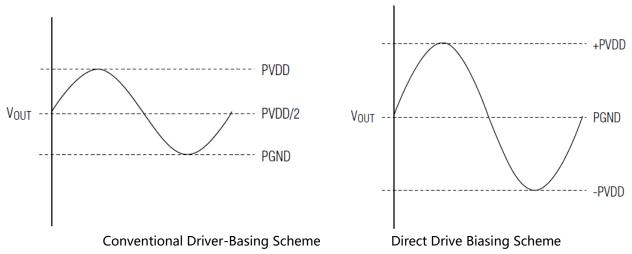

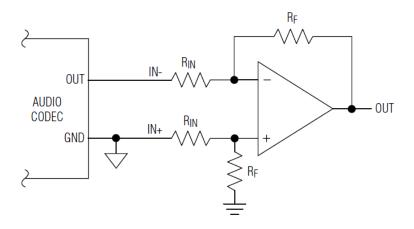

#### 2. Differential Input or Single-Ended Input

The IC can be configured as differential or single-ended input amplifiers (Figures 2 and 3), making it compatible with all codecs. A differential input offers improved noise immunity over a single-ended input. In devices such as cellular phones, high-frequency signals from the RF transmitter can couple into the amplifier's input traces. The signals appear at the amplifier's inputs as common-mode noise. A differential input amplifier amplifies the difference of the two inputs while signals common to both inputs are cancelled. The gain of the HT97180(L) is set by:

$$A_V = R_F/R_{IN}$$

The common-mode rejection ratio (CMRR) is limited by the external resistor matching, and if used, input capacitor matching at low frequencies. For example, the worst-case variation of 1% tolerant resistors results in 40dB CMRR, while 0.1% resistors result in 60dB CMRR. For best matching, use resistor arrays.

-11-

Fig. 2 Differential Input Configuration

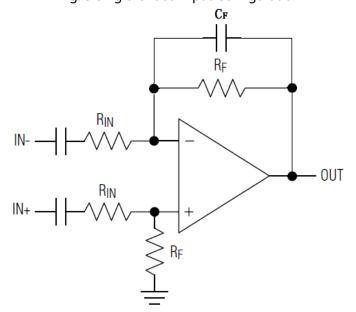

Fig. 3 Single-ended Input Configuration

Fig. 4 Add CF to keep system stable

The headphone has parasitic capacitance and If the parasitic capacitance is bigger than a certain value, it may cause the system out of stable. Fig. 4 shows that a capacity CF parallel with RF to keep the system more stable. Generally, a 6.8pF capacity is enough. However, if headphone's parasitic capacitance is very big, for example

bigger than 1nF, a bigger capacitance CF is needed. The CF can be 47pF or 68pF according to headphone's parasitic capacitance.

#### 3. Direct Drive

Conventional single-supply headphone amplifiers have their outputs biased about a nominal DC voltage (typically half the supply) for maximum dynamic range. Large coupling capacitors are needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both the headphone and the headphone amplifier.

HT97180(L) uses a charge pump to create an internal negative supply voltage, allowing the IC's outputs to be biased about PGND. With no DC component, there is no need for the large DC-blocking capacitors. Instead of two large (220uF, typ.) tantalum capacitors, the IC charge pump requires two small ceramic capacitors, conserving board space, reducing cost, and improving the frequency response of the headphone amplifier.

#### 4. Input Filters

In addition to the cost and size disadvantages of DC-blocking capacitors required by conventional headphone amplifiers, these capacitors limit the amplifier's low-frequency response and can distort the audio signal.

If input capacitors are used, input capacitor  $C_{IN}$ , in conjunction with input resistor  $R_{IN}$ , forms a high-pass filter that removes the DC bias from an incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the high-pass filter is given by:

$$f_{-3dB} = 1/(2\pi R_{IN}C_{IN})$$

Setting  $f_{-3dB}$  too high affects the low-frequency response of the amplifier. Use capacitors with adequately low voltage coefficients, such as X7R ceramic capacitors with a high voltage rating. Capacitors with higher voltage coefficients result in increased distortion at low frequencies.

#### 5. Bias Capacitor

Bypass BIAS with a 0.1uF capacitor to PGND. Do not connect external loads to BIAS.

#### 6. Charge Pump

The HT97180(L) features a low-noise charge pump. The 500kHz switching frequency is well beyond the audio range and, thus, does not interfere with the audio signals. The switch drivers feature a controlled switching speed that minimizes noise generated by turn-on and turn-off transients. By limiting the switching speed of the charge pump, the di/dt noise caused by the parasitic bond wire and trace inductance is minimized. The IC requires a 1uF flying capacitor between C1P and C1N and a 1uF hold capacitor from PVSS to PGND.

#### **Charge-Pump Capacitor Selection**

Use capacitors with an ESR less than  $100m\Omega$  for optimum performance. Low-ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric.

The value of the flying capacitor ( $C_{FLY}$ ) affects the charge pump's load regulation and output resistance. A  $C_{FLY}$  value that is too small degrades the device's ability to provide sufficient current drive, which leads to a loss of output voltage. Increasing the value of  $C_{FLY}$  improves load regulation and reduces the charge-pump output

resistance to an extent. Above 1uF, the on-resistance of the switches and the ESR of CFLY and CPVSS dominate.

The hold capacitor value and ESR directly affect the ripple at PVSS. Use a low-ESR 1uF capacitor for C<sub>PVSS</sub>.

#### 7. Click-pop Suppression

The IC features click-pop suppression circuitry. When entering shutdown, the amplifier outputs are high impedance to ground. This scheme minimizes the energy present in the audio band.

#### 8. Shutdown

The IC features a 1uA lower low-power shutdown mode that reduces power consumption. When the active-low shutdown mode is entered, the device's internal bias circuitry is disabled, the amplifier outputs go high impedance, and BIAS is driven to PGND. The HT97180(L) inputs are driven to PGND.

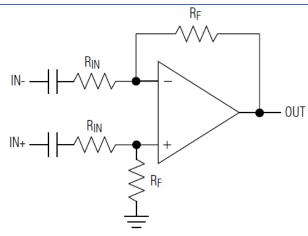

#### 9. Amplifier Gain

The gain of the HT97180(L) amplifier is set externally. The gain is:

$$A_V = -R_F/R_{IN}$$

Choose feedback resistor values between the  $4.7k\Omega$  and  $100k\Omega$  range.

There's another version of HT97180(L) that has an internally fixed 6dB gain needs to be pre-booked.

#### 10. Supply Bypassing

Proper power-supply bypassing ensures low-noise, low-distortion performance. Connect a 1uF ceramic capacitor from PVDD to PGND and a 1uF ceramic capacitor from SVDD to PGND. Add additional bulk capacitance as required by the application. Locate the bypass capacitor as close as possible to the device.

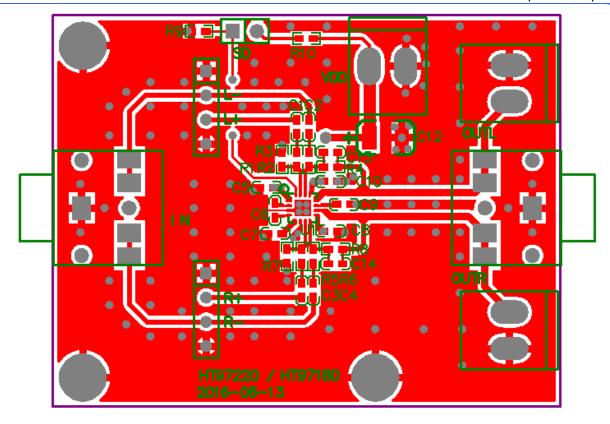

#### 11. PCB Layout and Grounding

Good PCB layout is essential for optimizing performance. Use large traces for the power-supply inputs and amplifier outputs to minimize losses due to parasitic trace resistance and route heat away from the device. Good grounding improves audio performance, and prevents any digital switching noise from coupling into the audio.

Connect PGND and SGND together at a single point on the PCB. Connect all components associated with the charge pump (C<sub>FLY</sub> and C<sub>PVSS</sub>) to the PGND plane. Connect PVDD and SVDD together at the device. Place capacitors CFLY and CPVSS as close as possible to the device. Ensure the PCB layout is partitioned so that the large switching currents in the ground plane do not return through SGND and the traces and components in the audio signal path.

The IC is inherently designed for excellent RF immunity. For best performance, add ground fills around all signal traces on top or bottom PCB planes. Also, ensure a solid ground plane is used in multilayer PCB designs.

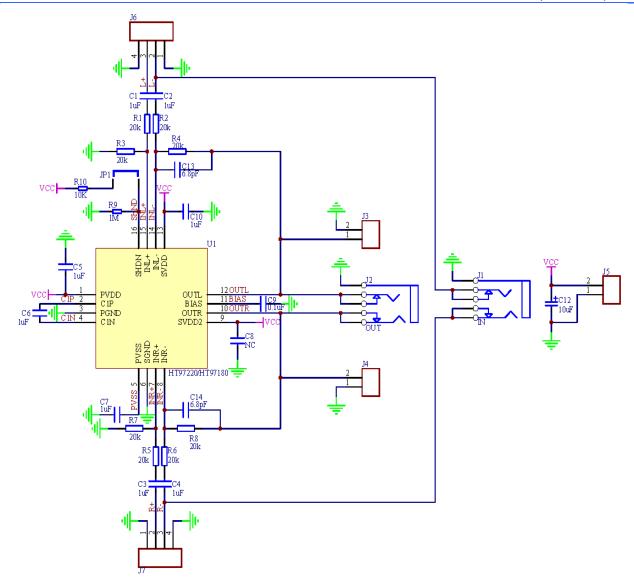

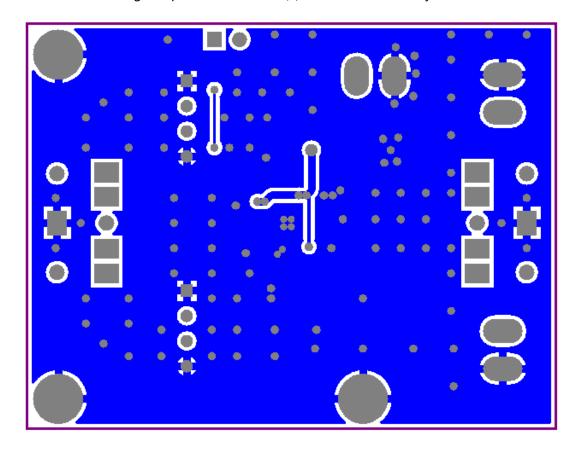

Fig.5 Typical Application of HT97180(L) Demo

Fig.6 Top View of HT97180(L) Demo Board PCB Layout

Fig.7 Bottom View of HT97180(L) Demo Board PCB Layout

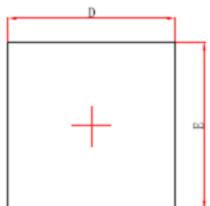

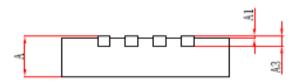

## ■ PACKAGE OUTLINE

| Symbol | Dimension in Millimeters (mm) |       |  |  |  |

|--------|-------------------------------|-------|--|--|--|

| Cymbol | Min.                          | Max.  |  |  |  |

| Α      | 0.700                         | 0.900 |  |  |  |

| A1     | 0.000 0.050                   |       |  |  |  |

| А3     | 0.203(REF)                    |       |  |  |  |

| D      | 2.900                         | 3.100 |  |  |  |

| E      | 2.900                         | 3.100 |  |  |  |

| D1     | 1.600                         | 1.800 |  |  |  |

| E1     | 1.600                         | 1.800 |  |  |  |

| k      | 0.200MIN                      |       |  |  |  |

| b      | 0.180 0.300                   |       |  |  |  |

| е      | 0.500TYP                      |       |  |  |  |

| L      | 0.300 0.500                   |       |  |  |  |