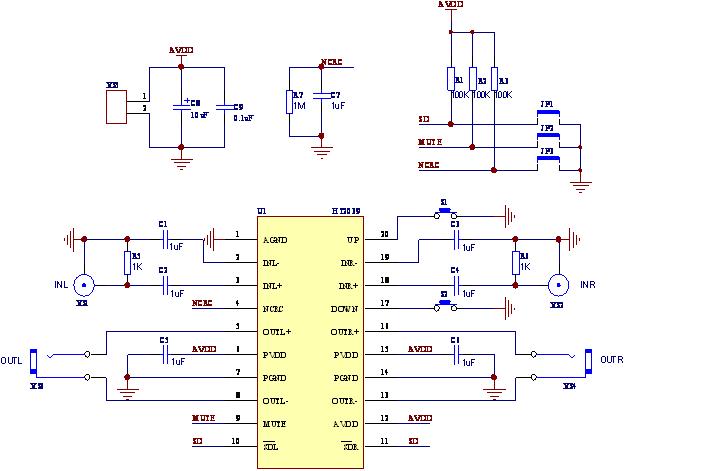

HT6809����ԭ��D

1�� D���EMI�ɔ_��Ҫ��ݔ���������a���ģ�������߅�����������裩�cHT6809 IC ݔ�������_֮�g��������ԓ�OӋ�رM���ܵĶ̣��֣��Ա��ڌ�EMI�ɔ_������С����һ���c�P�����B���������Ҳ�OӋ�Ĵ�һЩ���Ա��ڽ���ݔ���ˌ�ͨ��衣

2�� HT6809��GND�cݔ����̖��ؓ�������B��HT6809��GND��ԓ�cϵ�y��GND���B�����cݔ����̖��ؓ�˲����B���@�ӿ��Ա����·���Įa�������D��˜ʵĸ�GND�B�ӷ�����

.JPG)

һ����r���҂�����̖������ݔ�룬�@�ӿ������@�����o�룬����������Щ©��^����Դ�r�����ݔ��r���������˕r���Æζ�ģʽ���Խ��������ψD�����R?���Ǟ�̎��������r���A���ģ�����ʹ�ÕrNC��

3�� HT6809��VDD�˲���ע�������HT6809��PVDD�_�ɔ_�^���˲��ɔ_HT6809��AVDD��PVDDȡ��ϵ�y���Դ̎���Դ��ڣ�ȡ늣��Դ���̎�д���ݿ��Ԍ�PVDD�a���ļy���M�ОV�����V�����ٰ��Դ���oAVDD��ϵ�y��������Ҫ�Դ�ĵط����D��ʾ��D��

.JPG)

4�� Pin17�cPin20��ý�һ�w������裬ʹϵ�y�����ظ����������D��

.JPG)

Ԕ���ĮaƷ�Y��Ո��醣�http://www.wujiu5zhuce.cn/products_3368.htm |