����ժҪ

����������yʽ����O�䣬�����֙C�������C�����a���C��������X�ȶ���Ҫ��ه늳��S����������˾S���@Щ����O����m��������횷��͵ؽ������ͨ�^������팦����ıM��늳��M�г�늡����@�Ӵ�����Ԟ鳣��늳س���^�̅s�ڟo���Ў�����Դ�ēp��������Ҫ���µļ��g�����͟o�^���������ġ��e���ڴ��C�ĕr������_�����ܷ�Ҏ��Ҫ����������������Դί�T����California Energy Commission�� CEC������Ҏ�����Լ���Դ֮�ǣ�Energy Star�����RӋ���ȣ���˱�ƪ������̽ӑһ�����͘O�ʹ��C���ĵ��Դ����IC��

�����w���댧�w���Ƴ���FAN302HL������IC�����֙C������đ����п��_������10mW�Ĵ��C��Դ���ģ����ҽY�϶���I�ȼ��g����������������ʽ�D�Q�������ܣ��磺�Ƚ��߉������·�����C�r�ĵ���늉��c������������ôμ��˷������Ʒ����{���̶�ݔ��늉��������˷������Ʒ����{���̶�ݔ�������FAN302HL�����ɞ��ڴ��C�r�ĘO�����Դ����IC�OӋ����x��

��������

�����̓r�w�q��ԭ���σr��҄��¸ߣ�ȫ����Դ����l�R����߅����“���s��Դ”�ٴγɞ�����T���h�}�����ڭh�����^����m�����£��F���ˌ����ճ����s��Դ���^��Խ��Խ��ȫ�������s��Դ���˰Ѳ��õ�����P�]���Dz�ȡ���r�_�P��ʽ���s��Դ�⣬�䌍�@Щ����b�ñ������Դ�·�OӋ�����ơ�ƽ���_���\�������C���Դ�����������࣬ʹ����Դ�đ���Ч�ʵ��£���Ч���Դ����������“����”��Ч���������ҊӰ���Դ������������Ҫ��څ�ݣ�����ʹ���C���Ľ�����͡�һ������J�飬�c�����r�Դ�ĺ����������������O����C�r�����ĵ�������������䌍�@�c����ȥ���h����������������Դί�T����California Energy Commission�� CEC������Ҏ�����Լ���Դ֮�ǣ�Energy Star�����RӋ���ȣ��������Դ��Ҏ�����У�����“���C����”��Ҏ���O����ҕ������ڇ��H��Դ����IEA�����ƄӺͳ��������“1��Ӌ��”����ԴҎ����Ŀ���ǵ�2010�r��������aƷ�Ĵ��C���Ľ���1�ߣ�������Ҳ��2007��12���C����“2007������Դ�����c��ȫ����”�������M�����O���ƶ��˵�һ�������Ե�����Դ�˜ʡ�

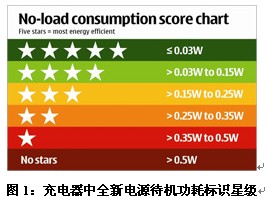

������������עĿ������2008��11��������Ҫ�֙C��؛�̹��������֙C������Ĵ��CҎ�������_���x����ͬ�Ĵ��C�����в�ͬ�Ę��R�Ǽ�����D1��ʾ�����֙C������Ĵ��C���Ę˜ʣ�����������w�ǵĴ��C���ı�횽�����30mW���£���ˣ�Ҫ���ʹ�Դ�D�Q���_�����͵Ĵ��C���ģ��������Դ�OӋ���̎�δ������Ҫӭ�ӵ�����

����

����FAN302HL���C���ā�Դ�����c�ʹ��C���Ľ�Q����

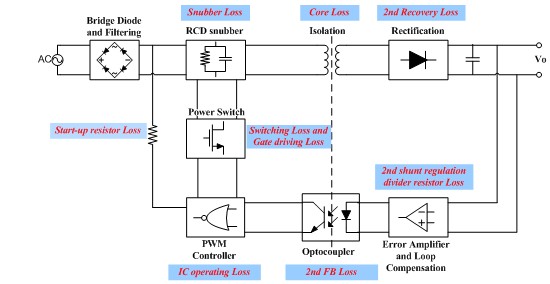

�������ʹFAN302HL�Ĵ��C���Ľ��͵�30mW���£������_������10mW��������Ԕ���ķ�����B�����ȿ������Ի������õķ���ʽ�D�Q�����Դ�ܘ�������������D2��ʾ��

����

�����D2�����͵ķ���ʽ�D�Q���·

����

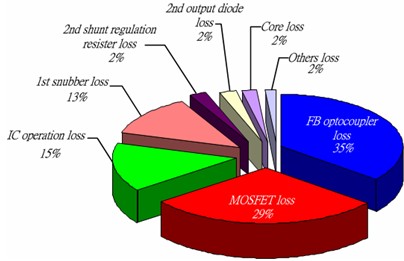

�����D3�����C���ĸ����ݵķ���ʾ��D

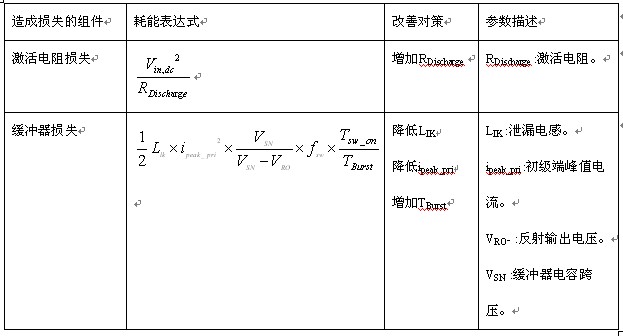

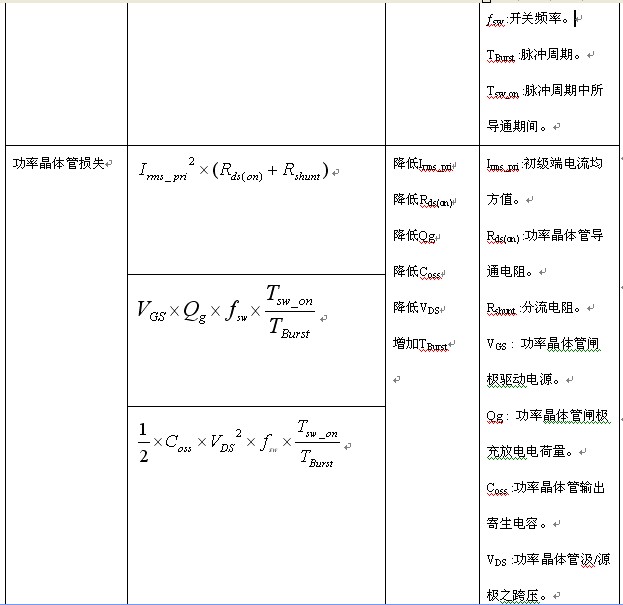

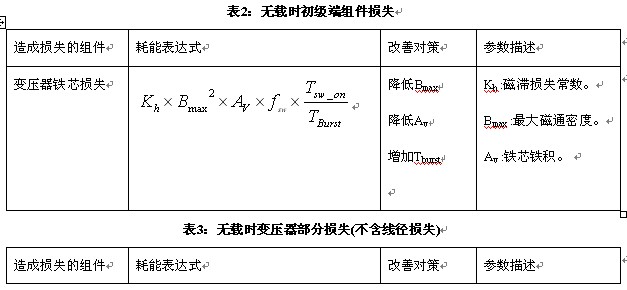

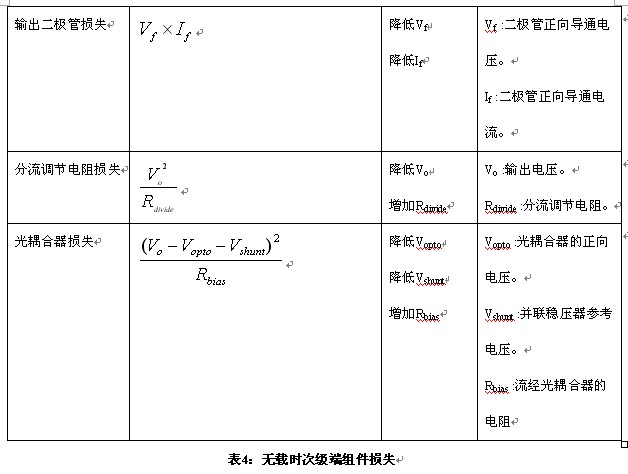

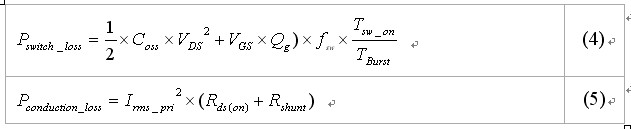

�����ĈD3�ɿ������C���ĵķֲ�����һ������ʽ�D�Q�����ԣ���Ҫ�Ĵ��C���İ������_�P���ģ�switching loss���͂������ģ�conduction loss���Լ�PWM�����·����ɵĹ��ġ���1����2����3����4�քe���@Щ��Ҫ���ģ��г����㹫ʽ�c���ƌ��ߡ�

����

����

����

����

����

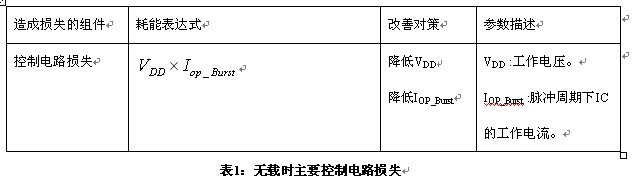

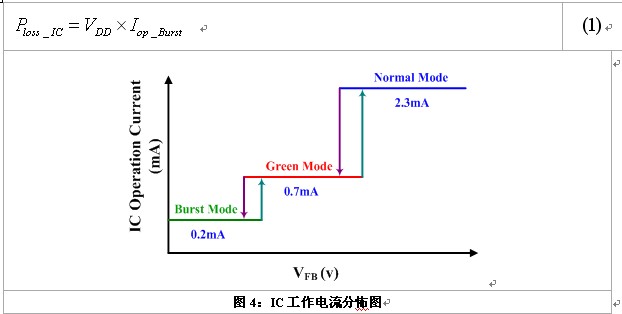

����1�������·�pʧ��15%�����ɱ�1�c��ʽ��1���п�֪���ڴ��C�r����ʹPWM IC�S�������Ĺ��������o����·�OӋ�ϱ�횴_�J�܉��ṩ����늉�������VDD��������FAN302HL�������늉���VDD_OFF����5V������ͨ���OӋ��7V����������롣����PWM IC����������棬FAN302HL���ж�ε�����������ƣ���D4��ʾ�����������}�_ģʽ��Burst mode���r�����ԘO�͵Ĺ��������������FAN302HL�Ĵ��C���ġ�

����

����2�������˽M���pʧ���ɱ�2�п�֪�������˽M���pʧ��Ҫ���ɼ������pʧ�����_���pʧ�c�������w����Power MOSFET�� �pʧ�Ŀ��͡�

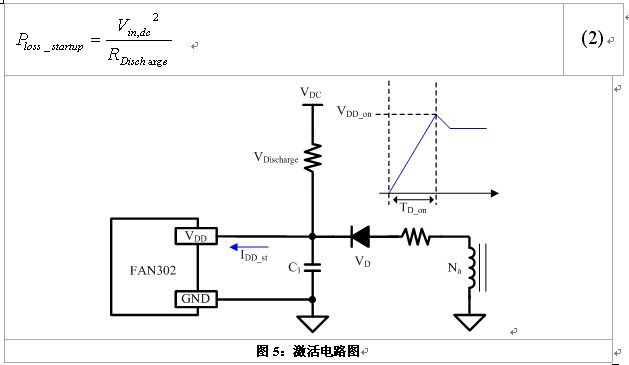

�����������pʧ��1%��������ʹPWM IC����������ǰ�ܫ@���Դ늉���ͨ�����O���м����·����D5����ʾ����PWM IC���o���@�M�@���Դ����֮�����·��ʧȥ���ã����˕r��������ϵĿ牺��Ȼ�����m��ɹ��ģ���ʽ��2����ʾ��FAN302HL�Ƚ��߉������·��HV��������y�����·���O�ã��ɜp�ټ��������ɵĹ��IJ��ɼ����_�C�r�g�c�߉��ļ���������

����

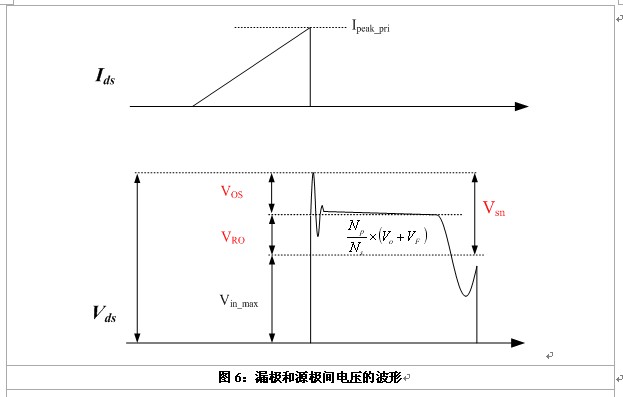

�������_���pʧ��13%���������ʾ��w���P�]��ͬ�r������©�O/Դ�O֮�g��늉���VDS���Ϯa���^�ߵļ��늉�����D6��ʾ���@������׃�����ϵ�й©늸������£���˱���й©늸еĮa���c��ֵ��������ӣ�������Ч�ظ������ēpʧ�����ʽ��3��

����

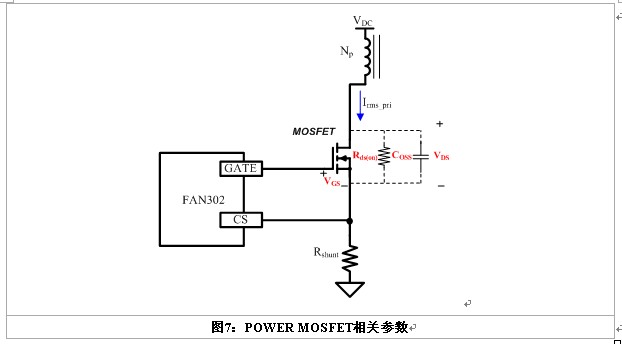

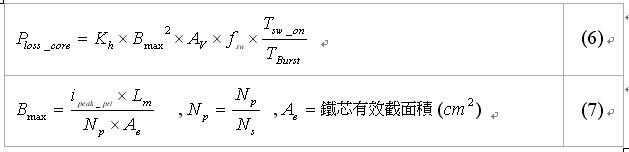

�������ʾ��w�ܓpʧ��29%�����ڹ��ʾ��w�ܓpʧ�IJ����У���Ҫ�������_�P�c�����pʧ�����ʽ��4����5����ʾ�������֙C������đ����������_�P�pʧռ���������˳������x���m�Ĺ��ʾ��w���⣬�����}�_ģʽ��Burst mode�����g���p�ن�λ�r�g�ȹ��ʾ��w�ܵ��_�P�Δ��������_�P�pʧ���S��ݔ��늉��ķ���������Ч���ƴ˲��ݵĹ��ģ��D7��Power MOSFET���P������

����

����

����3��׃�����Fо�pʧ��2%����׃������ݔ����r��������Ҫ�֞��~�p���F�p���~�p�dz������������׃������Ȧ�迹����ɵĺēp�������ڿ��d���C����r������׃������Ȧ�ϵ������С������ڴ˗l�����~�p��Ӱ푿ɱ����ԡ���5�c��ʽ��6�����О��F�p�Ĺ��Ĺ�ʽ����ʽ�п�֪�����_�P�l���c��ͨ�ܶȿ��Ը����Fо�pʧ�����{����ͨ�ܶȕr���ݱؕ�����є��ȣ�����Ȧ�є�����Ҳ�������~�p���������ʽ��7����ʾ�������Ҫ�������OӋ��о�Ĵ�ͨ�ܶȺ����l�ʁ��_�����ĵĸ���

����

����4���μ��˽M���pʧ���ɱ�4�п�֪���μ��˽M���pʧ��Ҫ����ݔ�����O�ܡ������{������c��������pʧ�Ŀ��ϡ�

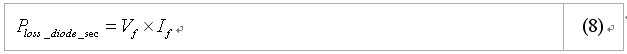

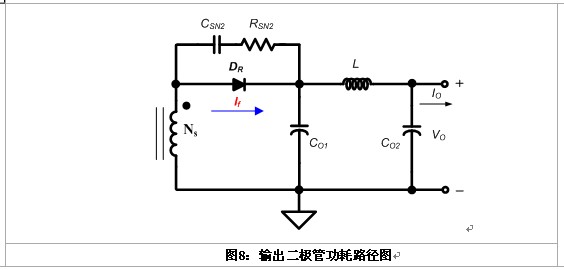

����ݔ�����O�ܓpʧ��2%�����D8��ʾ��ݔ�����O�ܹ���·��������������^���O�ܞ�����r�����cPN�ɘO�w�����a��������ͨ늉�����ɓpʧ�����ʽ��8����ʾ��������x�^������ͨ늉���ݔ�����O���DZ�l��֮һ��

����

����

���������{�����pʧ��2%���������ڷ����{�������轛�ɷ����{�����팧ͨ�������c�����λ�������^�����_���㶨ݔ��늉��������{������ԕ�ռ���������ģ����ʽ��9����ʽ���������{����������Ч���ƹ��ģ���ͬ�rҲ��Ӱ푵����������ȣ�������@���ݵ�ȡ��Ҳ��Ҫ�м����]���D9�鹦��·����

����

������������pʧ��35%������������Á��ṩ�μ��˵��������g��Ӎ̖���f���������ɔ_��ͬ�rҲ�ṩ�˷������Ƶ�Ӎ̖·����������������������Rbias�����ṩ�����������������������_�������Ĺ�����������������������������Ҳ����ϵ�y���һ���Ĺ��Įa�������ʽ��10����ʽ������@���ݵ�ȡ��Ҳ��Ҫ�úÿ��]��·���D��D9��ʾ��

����

����

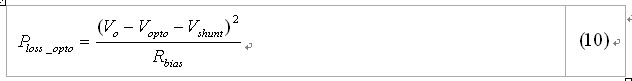

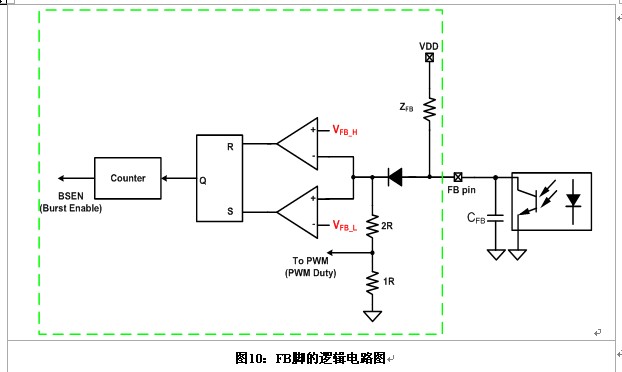

������������Փ�����Ժ����@�Ŀ������oՓ���_�P���ģ�switching loss���͂������ģ�conduction loss��������PWM�����·����ɵĹ��ģ��ݶ��c�_�P�l���к����е��Pϵ�������Ҫ����Ч�Ŀ��ƴ��C�r���a���Ĺ��ġ�FAN302HL�����}�_ģʽ��Burst mode���ļ��g�����_��ʡ늵�Ч����FAN302HL��ʹ�õķ�ʽ������FB���_��늉�׃�����Д��}�_ģʽ�Č�ͨ���ڣ��_���ڟo�d�r�ĘO�ʹ��C���ģ��ĈD10�п�֪FB���_����PWM�΄��{���⣬Ҳؓ؟�}�_ģʽ�΄յ��{������IC�������}�_ģʽ�rFB���_���Д�ԓ늉���λ���l���Ą�������VFB����VFB_L�r����ȥ�����P��PWMݔ����ʹ֮�o�������o�������}�_���ڣ��˕rݔ��늉�����Щ�½������VFB�ܿ���ߣ����Ԯ�VFB����VFB_H�r���ڏ��ƌ�ͨPWM���Թ��oݔ��������������˽�����\�����_�����m���}�_ģʽ�{�䡣�ĈD11�пɿ����}�_ģʽ�r�Ą���ԭ���c�}�_ģʽ�r�����P������

����

����

��FAN302HL�o�d���C����Ӌ�㌍��

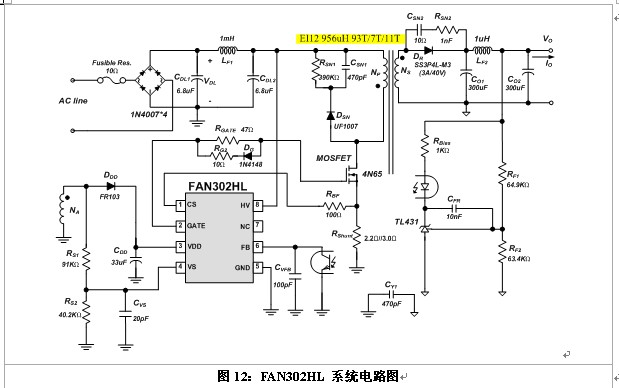

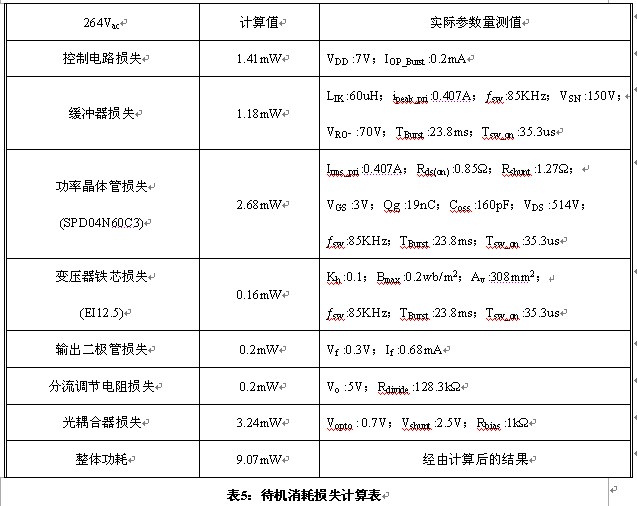

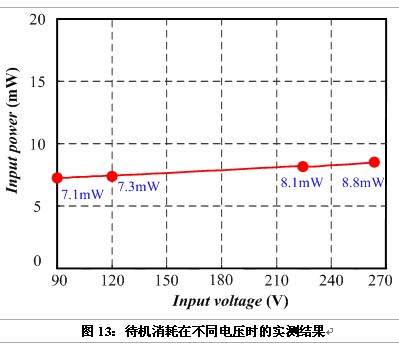

����ʹ���w�װ댧�w���аl���Ĺ���PWM IC��FAN302HL���������yԇ���ϣ���D12��ʾ�����~��ݔ��늉��c���Ҏ���5V/1A�����y���l���飻ݔ��264V����늉��������ڟo�d�����ɱ�5��Ӌ�������ֵ�����C���ļs9.07mW���˽Y���cϵ�y���H�yԇ�Y�����࣬�D13��ϵ�y���y�Y���D��

����

����

����

�����YՓ

�������Դ�I����Խ��Խ��Խ�����ژO�ʹ��C���ĵĮaƷ������˱�����Ҫᘌ��w�װ댧�w���Ƴ���FAN302HL�ӿ���IC��̽ӑ�����Դ���w���C���ĵķ������Ԕ��W��ʾʽӋ�����Ҫ���_�P�Ϳ����·�pʧ������B�ö���w�װ댧�w���µČ������gȥ���F���͵����w���C���ġ�������~��ݔ��늉�/���Ҏ���5V/1A��264V����ݔ����ݔ���o�d�r��ʹ���C���Ŀ����_��С��10mW�ĽY��������FAN302HL��IC���˿��Ԍ��F�O�ѵĹ��ܿ����⣬Ҳ�Ɍ��F���l������85KHz���c��Ч�ʹ������^�����ԝM���֙C������đ��ã��_��“�p����С”��Ŀ�ˡ� |