���˽ⲻͬ�ӿڵă�ȱ�c�����x��Ԫ�����@�����ڸ��Ӻ������x��Ԫ�������C��̖朵ĸ�Ч���F��

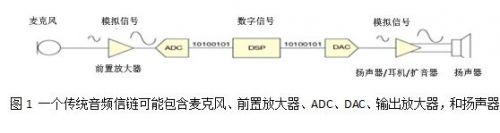

�S�����l�����·�D��������Ĺ�ˇ�߶ȣ�Ҫ����ͬһƬ���ܶȔ����·��Ƭ���OӋ�������ܵ�ģ�M�·׃�ø������y�����ɵ��ԃr�ȜpС����ˣ����lϵ�y�ܘ������ڌ����l��̖��е�ģ�M�����Mһ������ݔ����ݔ��ˣ�����g�Ԕ��a��ʽ�B��������

��D1��ʾ�����y�����l��̖����������L��ǰ�÷Ŵ�����ģ/���D�Q����ADC������/ģ�D�Q��(DAC)��ݔ���Ŵ������Լ��P��������֮�gʹ��ģ�M��̖�B�ӡ����ǣ�����ģ�M�·���Ƶ�����̖朵�߅������̖��и������·�g�����F�������ֽӿڡ�DSPͨ���ǔ����B�ӣ��Q�������Ŵ���һ�����ֻ��ģ�M�ӿڣ����F��Ҳ���ڰ������ֽӿڵĹ��ܡ�

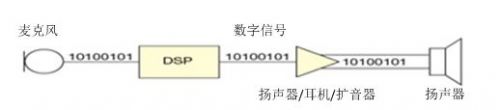

Ŀǰ�������·�OӋ�ˆT���ڌ��Q�����ȵ�ADC��DAC���{�������ɵ���̖朵���һ�ˣ��@�ӾͲ�����ӡˢ�·��(PCB)�ϲ����κ�ģ�M���l��̖�����Ҝp������̖��е������������D2�o����һ�������������l��̖朵����ӡ�

�������l������ݔ�F�����S���˜ʡ��ܶ��ʽ������������ͬһ�KPCB�ό��FIC�g��ͨ�ţ���I2S��IC�g���l����TDM���r�֏��ã���PDM���}�_�֕r���ã��ȸ�ʽ���������l��ʽ�t��Ҫ����ͬӡˢ�·��֮�gͨ�^��|�Ĕ����B�ӣ���S/PDIF����̫AVB��

���ĵ����c��IC֮�g�������l��ʽ�ą^�e�c��ȱ�c�����x���˔��ֽӿڲ�ƥ������l�M�����t������Ҫ��ʹϵ�y�OӋ׃�ø��ӏ��s���˽ⲻͬ�ӿڵă�ȱ�c�����x������������߽M���x��Ч�ʺͱ��C��̖朵����Ч���F��

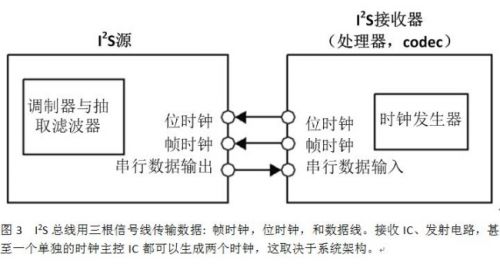

IC֮�g���l(12S)�����ڼ����·֮�g���l������ݔ���Ҋ�������l��ʽ���w���ְ댧�w�����F�ڵĶ����ְ댧�w����1986���Ƴ���12S�˜ʡ�1996�ꌦԓ��ʽ�M������ӆ��ԓ�ӿ��״ΏV��������CD���������OӋ,�F�ڎ����漰�����·�g�������l�����D�Q���κΑ����϶����Կ���ԓ�ӿڡ��������lADC��DAC��DSP���c�ɘ������D�Q�����Լ�һЩ������������I2S�ӿڡ�

һ��I2S������ʹ��������̖����������ݔ�����r犣�λ�r犣��Լ�������������IC���l��IC������һ���Ϊ��ĕr�����IC���������Ƀɂ��r犣��@ȡ�Q��ϵ�y�ܘ�(�D3)������I2S�˿ڵļ����·ͨ�������O�Þ���ģʽ���ģʽ�������OӋ����̖���ʹ���˲ɘ����D�Q������tϵ�yͨ�����І�һ��I2S���O�䣬�Ա�����F����ͬ�����}��

�����@Щ��̖���w���֘˜��Ќ����x��������WS���r�������SCK������������SD��Ȼ���·�������ƺ��������Լ���IC��������ʹ���@Щ���Q�����x�����Q��LRCLK����ʾ“��/�ҕr�”����SCK�t���Q��BCLK��ָλ�r犣����SCLK�������Еr犡�

IC���Д������_�����Q��ͬ���·�����̶���ͬ������ͬһ�������̸��aƷ�g������Ҳ��ͬ�������lIC��������һ�ݿ����{���@ʾ��SD��̖Ҳ���ԷQ��SDATA��SDIN��SDOUT��DACDAT��ADCDAT�����@Щ���Q������׃�w��ȡ�Q�ڔ������_��ݔ��߀��ݔ����

I2S�������܉���һ������λ�r����ʣ��y��һ����ɂ�ͨ���Ĕ��������͵�λ�r�����512 kHz������8 kHz�ɘ����ʣ��c12.288 MHz����192 kHz�ɘ����ʣ�֮�g�������ֵ��L��ͨ����16��24����32λ������С��32λ�Ĕ������L�����L��һ��߀��64λ���]���õ���λ�ɰl��IC�������ƽ��

��ЩIC�H֧��ÿ�����w���l�����32λ��48λ�r犵Ľӿ�I2S���mȻ����Ҋ�����ʹ���@�IC��ϵ�y�OӋ�ˆT�ͱ�횴_�����B����һ�˵��O��Ҳ֧���@Щλ�r��ʡ�

�D2 IC�OӋ�ˆT���ړQ�����е�ADC��DAC���{�������ɵ���̖朵���һ�ˣ��Ķ��o����PCB���ϲ���ģ�M���l��̖�����p������̖��ϵ������������D����һ�������������l��̖朵����ӡ�

�M��I2S���ʹ�õĸ�ʽ����Ҳ��������ͬ�����Y����׃�w�������R���Ҍ��R��PCMģʽ���@Щ��ʽ�cI2S�ą^�e���ڎ��Д����ֵ�λ�á��r犵ĘO�ԣ���ÿ������λ�r����ڵĔ�����

TDM��ʽ

��ЩIC֧��ʹ��һ�������r犵Ķ�·I2S����ݔ���ݔ�������@�ӵķ����@Ȼ�����Ӕ�����ݔ����Ҫ�Ĺ��_��������ͬһ���������ς�ݔ�ɂ�����ͨ���Ĕ����r����Ҫʹ��TDM��ʽ��TDM���������Գ��d���_16ͨ���Ĕ���������һ�������I2S�Ĕ���/�r犽Y����

ÿ��ͨ���Ĕ�����ʹ�Ô��������ϵ�һ���ۣ�Slot�����䌒���ஔ�ڎ���1/N, ����N�ǂ�ݔͨ���Ĕ��������ڌ��ÿ��]��Nͨ���������뵽�����2��(2��4��8����16)�������κζ���ͨ���������e��һ��TDM���r�ͨ�����F��һλ�����}�_���@�cI2S��50%ռ�ձȕr��෴�����^25 MHz�ĕr�����ͨ��������TDM������ԭ�����^�ߵ��l�ʕ�����ӡˢ�·���OӋ��Ҫ����İ��沼�ֆ��}��

TDM�����ڶ���Դ����һ��ݔ��ˣ����Դ�Ӷ�ֻ������ϵ�y����ǰһ�N��r�£�����Դ����һ��ݔ���)��ÿ��TDMԴ����һ�������Ĕ���������ԓ��Դ������Þ������m��ͨ�����g���ӿ������������������������������r��������Ҫ�Þ����B��

TDM�ӿ�߀�]���F����w����I2S�������˜ʣ���ˣ��ܶ�IC�������Լ�����ͬ��TDM���F�������@Щ׃���w�F�ڕr犘O�ԡ�ͨ�����ã��Լ��e��ͨ�������B�������ϡ���Ȼ��ͨ����r�²�ͬIC�ǿ���һ�����ģ���ϵ�y�OӋ�߱�횴_��һ��������ݔ����ʽҪ������һֻ����ݔ��˵��A��

PDM�����B��

PDM�����B�����֙C��ƽ����X�ȱ�y���l�����Ϸ���׃��Խ��Խ�ձ顣PDM�ڳߴ����ޑ����Ѓ������@����������Ԍ����l��̖�IJ��Ň��@LCD�@ʾ���ȸ����·��������̎��ģ�M���l��̖�������R�ĸɔ_���}��

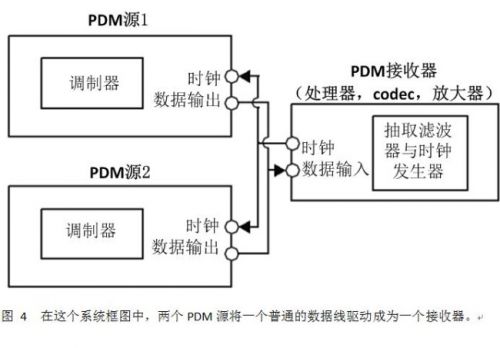

����PDM���H�ɸ���̖���Ϳ��Ԃ�ݔ�ɂ����lͨ������D4ϵ�y��D��ʾ���ɂ�PDMԴ��һ�������������Ӟ�һ����������ϵ�y��������һ���ɱ��ɂ����O��ʹ�õĕr犣��@�ɂ����O�佻��ʹ�Õr犵�߅����ͨ�^һ��������̖�����䔵��ݔ����ȥ��

�@Щ�����{����һ��64×�����ϣ��Ķ��γ�һ��ͨ����1��3.2 MHz�ĕr犡����l��̖�����S���r��l�ʵ����Ӷ����ӣ���ˣ�������ϵ�y��ʹ���^���l�ʵĕr犣��Ķ������˞鹝ʡ���Ķ����͵Ď�����

����PDM�ļܘ���ͬ��I2S��TDM֮̎�ǣ���ȡ�V�����Dz��ڰl��IC�У�����λ�ڽ���IC�С�Դݔ����ԭʼ�ĸ߲ɘ����{�Ɣ�������Sigma-Delta�{������ݔ������������I2S���ǘӵij�ȡ����������PDM�ļܘ��p����Դ�����ď��s�ԣ�ͨ���������ѽ������ھ���a��ADC�еij�ȡ�V������

ͨ�^�@�N����,ϵ�y�OӋ�߲��H�������ÿ����ѱ�ʹ�õ����l����a��, Ҳ�������õ����֔����B�ӌ��ɔ_�����еă��c�����⣬ͨ�^ʹ�����a����̎��������ĸ������蹤ˇ�߶ȣ�����������ԒͲIC�Ĺ�ˇ���Ϳ��Ԍ��F����Ч�ij�ȡ�V������

����a����DPS���ͷŴ�������I2S�˿ںܶ����ˣ���ֱ���F�ڣ������L��ϵ�yݔ���O��߀��ģ�M��PDMݔ�����S�����ֽӿ��Mһ��������̖朵ăɶˣ�����Ҫ�µ�IC��֧���µ�ϵ�y�ܘ���

���м���I2S�ӿڵ�ԒͲ����Analog Devices��˾��ADM441 MEMSԒͲ��ʹ�OӋ�ߺ�����ԓԪ������������ʹ��PDMԒͲ��ϵ�y�У���ϣ����ģ�M�ӿڵ�ϵ�y�С�ֻ���ٲ������l����a���ܽ���PDMݔ�룬�O�ٌ��Tᘌ��֙C��ƽ����X�OӋ��̎��������ԭ���ؽ����@�N��͔�������

����Щ�OӋ�У�һֻI2Sݔ����ԒͲ������ȫ�o���κ�ģ�Mǰ���·����˺ܶ��OӋ����ֻ��һֻADC��PGA���Ķ�֧��ԒͲ��̎�����Ć�ݔ�롣�@��һ��ϵ�y�Č�����һ�N�������l�����ğo��ԒͲ���o����ݔSOC���ܲ��]�Ѓ���ADC����˲���һ��I2SԒͲ�����܌��F�Q�����c�l����֮�g����ȫ���ֻ��B�ӡ�

I2S��TDM�cPDM���l�ӿڸ����䃞�c�c���m�ϵđ��á��S���������lIC��ģ�M�ӿ��D���ֽӿڣ�ϵ�y�OӋ���c�ܘ���������Ҫ�˽��ķN�ӿ����m�����Լ����ض��OӋ����ԒͲ��DSP�ٵ��Ŵ������@��һ��������̖朿�����ȫÓ�x�_PCB�����H���������l���С�