��(sh��)ģ�����̖�·�ĵ����O(sh��)Ӌ

1�������·�ĵ����O(sh��)Ӌ����

�ڼ����·�l(f��)չ�����ڵ������o��ʮ��������Ć��}�����Ǻ�ͻ�������@�Εr�g��(n��i)�������·ϵ�y(t��ng)Ҏ(gu��)ģ�ձ��^С��CMOS��ˇ���d�𣬵�����δ������IC�O(sh��)Ӌ����Ҫ���ء�

��1968�꣬Intel��˾�Ą�(chu��ng)ʼ��֮һG. Moore���A(y��)�y��ÿ18��24���£�IC�ļ��ɶȌ����һ�����@����������Moore���ɡ������ϣ��@��ʮ�������IC���g(sh��)���ǻ�������ѭ��Moore����ȡ���˾�İl(f��)չ�������·��(j��ng)�v�ˏ�СҎ(gu��)ģ���ɣ�SSI���l(f��)չ������Ҏ(gu��)ģ��VLSI�����F(xi��n)�ڵ�����Ҏ(gu��)ģ���ɣ�ULSI������һ��оƬ�Ͽ�����һ�|���ϵ�Ԫ����ˮƽ���mȻ����Ч��(y��ng)�ͽ�(j��ng)�������ƌ�ʹIC���ɶ����L���ٶ�څ�������ǿ����A(y��)Ҋ���ǣ��S���¼��g(sh��)�IJ���IC�ļ��ɶȳ��m(x��)�l(f��)չ�Ą��^��������׃��ͬ�r��ϵ�y(t��ng)�ď�(f��)�s��Ҳ�ڲ������ߣ�������ͬ���ܵ��������·�����ɵ�һ��оƬ�ϣ���(g��u)��һ��ϵ�y(t��ng)����оƬ��SOC�����@Ȼ�������·��(f��)�s�Ⱥͼ��ɶȵ����ʹ�õ������ɞ�һ�����ɻ�ȱ���·�O(sh��)Ӌָ��(bi��o)��

���ȣ��^�ߵĹ��Č�ʹоƬ�����^�ᣬ�·�ɿ����½�����K��(d��o)��ʧЧ�����о��������ض�ÿ����10 C�������Ĺ����ʌ���߃ɱ������⣬�������ߵĹ��Č��oоƬ�ķ��b��ɢ������˸��ߵ�Ҫ���@���H�����ӳɱ���������С�ͻ���(y��ng)�È����У��@�N�������������ɼ{��

����Ҫ���ǣ����M���Ӯa(ch��n)Ʒ�İl(f��)չ�ʹ�����(y��ng)���Ƅ��ˌ����Ć��}���о���

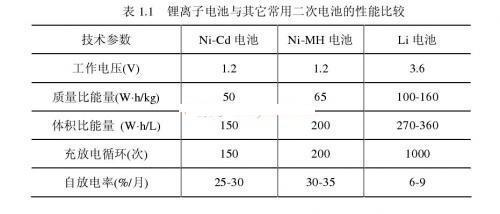

���ĵĸ�����������ֱ��ȹ��I(y��)�״�����ģ�����С�ͻ������ɶȵ����M���Ӯa(ch��n)Ʒ�У����˽����·�ɱ�������·��(w��n)���ԡ��ɿ��ԣ�����Ҫ�O(sh��)Ӌ�����·���Ա��C�ڼ��ɶ���ߕr����λ��e�S��ͬ���������͵Ĺ��ġ�ͬ�r��������^ȥ����ʮ����늳ص������H�H������2��4�����h�]��VLSI���g(sh��)�İl(f��)չѸ�٣�������늳ع��ϵ�y(t��ng)�У������·�ĵ����O(sh��)Ӌ�����L늳�ʹ�É���������Ч�ֶΡ����⣬��yʽ�O(sh��)��څ��ʹ�ø��ٵ�늳أ��ԜpС�ߴ��������Ҳ��ȻҪ���·���F(xi��n)���ġ���ʮ��ǰ��ȣ����M���Ӯa(ch��n)Ʒ����Ӯa(ch��n)�I(y��)�еı����я�40%�������L��55%����˿����f���M���Ӯa(ch��n)Ʒ�ǵ����O(sh��)Ӌ����Ҫ�Ƅ�����

2����(sh��)ģ�����̖�·�ĵ����о�

���@�N���g(sh��)����ͱ�yʽ��Ӯa(ch��n)Ʒ�đ�(y��ng)������ď����Ƅ��£�CMOS�����·�͉������O(sh��)Ӌ�ܵ����˂��ĘO����ҕ��Ŀǰ���˂��������·�Ĺ����о�����Ҫ���������ɂ����棺

һ�ǵ��Ĺ�ˇ���о����@��Ҫ�����ڜpС�����ߴ硢�����Դ늉��ͽ����ֵ늉����档�pС�����ߴ磬�����ڌ���(f��)�sϵ�y(t��ng)������ͬһоƬ�ϣ��M����Ч�ع��Ĺ��������Ǯ�(d��ng)�����ߴ�sС��һ���̶ȣ����d����Ч��(y��ng)���ӑB(t��i)��(ji��)�c��ܛʧЧ���O���Ӱ������������ܣ������Դ늉��ɞ��Q�������}���^�÷��������˱��C�͉�߉�·���(q��)��������p�ٺ����l�ʲ����ͣ��ڽ����Դ늉���ͬ�rҲҪ���ֵ늉�������ͬ���������ֵ늉���ʹ©й���ָ��(sh��)�����ӡ����ö��ֵ늉��������Dz��ÿ�׃�ֵ늉����g(sh��)�����pС©й�������Ĺ��ģ����@Щ���g(sh��)�����^��ه���칤ˇ��

���ǵ����O(sh��)Ӌ�������о����@��Ŀǰ�����о��������S���I(l��ng)���ڹ�ˇ�_������r�£����������ĵ��O(sh��)Ӌ�������u������������Ҫ��ᘌ���(sh��)���·��

�ڱ��Cϵ�y(t��ng)ͬ�����ܵ�ǰ���£���оƬ�O(sh��)Ӌ�ij��ڣ��͏ĸ����ӴΌ������M�з�����(y��u)�������H�܉�s���O(sh��)Ӌ���ڣ�߀�܉�?q��)��F(xi��n)���w������С��Ŀ��(bi��o)�����O(sh��)Ӌ�ĽǶȣ������O(sh��)Ӌ�������Էֳ�ϵ�y(t��ng)����System Level�����㷨/�Y(ji��)��(g��u)��Architecture/Algorithm Level�����Ĵ�����ݔ����Register Transfer Level��RTL����߉/�T����Logic/Gate Level������D����Layout Level���@�ׂ��ӴΡ����У�ϵ�y(t��ng)���㷨������ļ��g(sh��)�еĸߌӴΣ���ϵ�y(t��ng)���ĵ�Ӱ푺ܴ����@�N�Ӵ��ϵĹ��ķ������܌�ϵ�y(t��ng)�����M���A(y��)�y����(y��u)�������܌��F(xi��n)�ׂ���(sh��)�����Ĺ��Ľ��ͣ���˱�횼�����ҕ��

��Ч�Ĺ����u�����ߺͷ����ǵ����о�����һ����Ҫ��(n��i)�ݡ�������O(sh��)Ӌ�IJ�ͬ�ӴΌ��·�����M�п��ٜʴ_�ع�Ӌ��Ҳ�Ǽ����·�O(sh��)Ӌ�е�һ�����c���y�c���}��ͨ�����ѹ����u���֞�����S�C�y(t��ng)Ӌ��ģ�M�ķ����@���

�����S�C�y(t��ng)Ӌ�Ĺ��Ĺ��㷽���������˼��飺�ȸ���(j��)ģ�K�İ�D��߉��������ȡ�·��߉ģ�ͣ�Ȼ�����S�C�a(ch��n)����ݔ����ģ�M��Ӌ��ƽ�����ġ�

���ă�(y��u)�c���ٶ��^�죬���Ҳ���Ҫ�·��(n��i)����Ϣ�������Ĺ���ʴ_�̶Ȳ�������ģ�M�ķ���������m����ͨ���O(sh��)Ӌ�������A�Ρ�

����ģ�M�Ĺ��Ĺ��㷽������һ�M���͵�ݔ��ʸ���M�й���ģ�M���ԫ@��ƽ�����ġ���ļ���С����ֵ������ģ�M�ķ������ȸߣ�����ռ�惦���g��ģ�M�r�g�^����˿�����һЩ���l(f��)��Ϣ�������Ք��������ؿ��_��Monte Carlo��

ģ�M�������z���㷨�����У����ؿ��_���������·ݔ����S�C�a(ch��n)��ݔ����̖������ģ�M����Ӌ����ijһ�r�g�g���(n��i)�Ĺ��ġ�������F(xi��n)�е��·�����T����ģ�M�����������ؿ��_����ă�(n��i)�h(hu��n)�����܉�?q��)��F(xi��n)�ٶȺ�Ӌ�㾫�ȵ����ԡ����͵Ļ���ģ�M�����Ĺ��ķ���ܛ����POWERMILL��Entice-Aspen�ȡ�

��Ҫָ�����ǣ�Ŀǰ�ĵ����о�����nj�ģ�M�͔�(sh��)���·�M�з��_ӑՓ���@��ģ�M�·���������c�������P(gu��n)��ģ�M�����·��̎��0��1��̖�Ĕ�(sh��)���·��ͬ������Ҫ̎�����ȡ��r�g���l���B�m(x��)׃������̖�����Ҿ����������c��

���·��ʽ�Ķ����ԡ�������(sh��)��(j��)�D(zhu��n)�Q������A/D�D(zhu��n)�Q����D/A�D(zhu��n)�Q���ȣ����\��Ŵ��������ԷŴ����������Ŵ����������Ŵ����ȣ����Ǿ��ԷŴ�����ģ�M�˷���������(sh��)/������(sh��)�Ŵ����ȣ�����·ģ�M�_�P(gu��n)���Դ늉��{(di��o)��(ji��)���������{(di��o)�������_�P(gu��n)�Դ�������ȣ������ܹ���IC�Լ������IC.

������ָ��(bi��o)�Ķ����ԡ��������ȡ�ݔ�뷶����ʧ�桢�����Դ늉����Ʊȣ�PSRR�������桢�l�ʎ�����ݔ��/���迹�ȡ�

���·�Y(ji��)��(g��u)�Ķ����ԡ��H��һ���\�Ş��������Ѓɼ���Cascode���ۯBʽ��Folded��Cascode��A/ABŴ������ζ�/��ַŴ����ȱ���Y(ji��)��(g��u)��

�������Ķ����ԡ���Ҋ���������о��w�ܡ����O�ܡ���衢��ݡ�����늸еȡ�

ģ�M�·̎����̖���B�m(x��)�ԡ��·�Y(ji��)��(g��u)��ʽ�Ķ����ԡ�����ָ��(bi��o)�ľ��_�ԣ���ʹ���·����D���O(sh��)Ӌ��횇��@���w�·չ�_���O(sh��)Ӌ���Ԅӻ��̶��h�h���ڔ�(sh��)���·�����y�����h���ں��ߡ�

�mȻ�ڔ�(sh��)�֕r������(sh��)���·���O(sh��)Ӌ��������ˇ�l�����I(l��ng)����ģ�M�·����(sh��)��IC���Ј�ռ����ҲҪ����ģ�MIC����ģ�M�·�����ǔ�(sh��)���·�ͬF(xi��n)������Ę�������������Ȼ�����İl(f��)չ���g�����⣬�ڌ��H���^�ߏ�(f��)�s�ȵ�ϵ�y(t��ng)�У����ǰѴ惦�·��߉�����·��ģ�M�·һ����ͬһоƬ�У������^�Ĕ�(sh��)ģ����·��CMOS��ˇ�ij�����ڔ�(sh��)���·�е��ձ鑪(y��ng)�ã�ҲҪ��ϵ�y(t��ng)��ģ�M�·��ˇҪ�͘�(bi��o)��CMOS��ˇ���ݣ���ˣ�ģ�M�·�а��������ڃ�(n��i)�����܌�ֱ�ӛQ����ϵ�y(t��ng)�����ܡ�

�ڻ����̖�·�У��S��ɹ���(y��ng)���ڔ�(sh��)���·�еĵ��ļ��g(sh��)�������m�ϑ�(y��ng)����ģ�M�·�С����磬�����Դ늉��ǜpС���ĵ���Ч������������ģ�M�·���o���ĄӑB(t��i)��������������控���˷e�������Դ늉�������ʹ�������ߣ��@ͬ�rҲ�f�����ڵ�늉����F(xi��n)���ģ����Ԡ����·��һ�������ܞ���r�ġ����ģ�M�·�����ܲ���Ó�x���w���·��ӑՓ���������^����īI����˵͉������·�O(sh��)Ӌ��

�S��Խ��Խ���늳ع�는�(sh��)ģ����·�ij��F(xi��n)���������y(t��ng)���O(sh��)Ӌ�����ܵ��ˏ��ҵ�����(zh��n)�����ı�ȻҪ�����������̖�·�M�нy(t��ng)һ�Ĺ��Ĺ����������nj�ģ�M����(sh��)���·�����_�������O(sh��)Ӌ�ĽǶȣ���΅f(xi��)ͬ���]��(sh��)�֡�ģ�M�·�Ĺ��ģ��������ȼ���(sh��)���·��ģ�M�·��������y��