С�����l�l�ʺϳ����ڜyԇ�r������һ���h·�V�����·�c������ʎ�����ܘ���һ���������i��h�·��������·�Эh·�V�������OӋ�ÉČ�ֱ��Ӱ푵�оƬ�����ܜyԇ����ADF4153С�����l�l�ʺϳ����������о���������h·�V�������OӋ�������o���˻���оƬ�yԇ�ĭh·�V�����OӋ���̣����M������C�yԇ���yԇ�Y��������ԓ�V�����ɝM��С�����l�l�ʺϳ���оƬ�yԇ����Ҫ��

���M��С�����l�l�ʺϳ�����оƬ�yԇ�r�����ֲ��ֿ���ͨ�^��Ҏ�Ĕ��֜yԇ���������Ԍ��F����ݔ�����l��̖����λ�����sɢ���t��ҪоƬ������������ݔ����B�²��ܜyԇ��С�����l�l�ʺϳ���оƬ�ڜyԇ�r��Ҫ�c��ӭh·�V������LF����������ʎ����VCO�����ܘ����������i��h��·���ھ߂�������оƬ���ܵ�ǰ���²��܌��F������λ�����sɢ���µĜyԇ��

һ����ԣ�������ʎ����ʹ�ìF�ɵ������������x�����rע������ָ�˵�ƥ��Ϳ��ԣ�ֻ�Эh·�V����������ҪӋ����OӋ�ġ��h·�V�����������·����Ҫ����һ����ͨ�V����������оƬ�b����ݔ�����}�_��̖�M�е�ͨ�V���������l�����V������K�õ�һ������ƽ����ֱ��늉���̖ȥ����VCO�������Ķ��@��һ���������l��ݔ�����h·�V���������܌�ֱ��Ӱ푵�С�����l�l�ʺϳ���оƬ���ܵĜyԇ��

������ADF 4153��С�����l�l�ʺϳ����������o���������F�����A�h·�V�������OӋ�������܉�M��оƬ���H�yԇ����Ҫ��

1��ӭh·�V�������OӋ

�h·�V������늺ɱ��i��h�·����Ҫ�h�������B����늺ɱú͉�����ʎ��֮�g���i��h�Ļ����l���������ɭh·�V�����Q���ġ����H�ϣ��������ڭh·�V�����Ĵ��ڣ��i��h�ſ����x����������������l�ʺ͎����ȡ��h·�V��������Ͷ�N���ӣ����·֞���Դ�V�����͟oԴ�V�����ɴ���oԴ�V�����c��Դ�V������ȣ��䃞�c���ڣ��Y�����Ρ��������߷����Ⱥ����Ԍ��F��

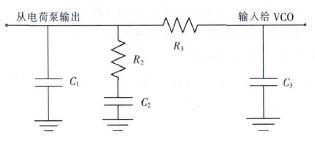

�Ҋ�ğoԴ�V��������D1��ʾ�����A�V������һ����ԣ��h·�V�����Ď�������PFD�l�ʣ�ͨ���g������1/10.��߭h·�������s���i���r�g�����h·�����^�������ȵ����Ӳ������ԣ��Ķ������i��h�o���i���Ġ�B��

�D1���A�h·�V����

���A�oԴ�V�����Ă��f�����飺

������ȡC1��C12��C3��R1��R2��ȡֵ��������Ҫ�_���OӋ��Ҫ�Ď�������λԣ�ȣ��T���īI�o����Ԕ������ȡ���E���ڴ˲��ٷ�����Ȼ�����ڌ��H�đ��Õr���@�NӋ�㷽���^�鷱���������ڹ����OӋʹ�á�

ADI��˾�l����ADIsimPLL�l�ʺϳ����OӋܛ�����Ժܷ���ظ����Ñ���ʹ��Ҫ���M�Эh·�V�������OӋ���������ù��̎��ķ��s�Ĕ��WӋ���н�Ó������������ֻҪݔ���O�íh·�V�����Ďׂ��P�I������ADISimPLL�Ϳ����Ԅӵ�Ӌ�������Ҫ�ĞV����Ԫ�����Ĕ�ֵ���@Щ�����������b���l��PFD��늺ɱ����ICP���h·����BW����λԣ�ȣ�VCO�����`����Kv���V��������ʽ����Դ��oԴ���A������Ȼ������оƬ�yԇ�r����αM���ܵ،�����·����h·�V����������������ͣ��Ԝyԇ��оƬ���挍���ܣ��@��оƬ����·�OӋ�r��Ҫ��Q�Ć��}��

2�h·�V�����OӋ�������x��

�����о��h·�V�������i��hݔ���l����λ����Ӱ푣��OӋ������оƬ�yԇ��Ҫ������h·�V�������҂���ADIsimPLLܛ�����M�������·������á�������̖��ADF 4153��fPFD=25MHz��������̖Դ����INT=69��FRAC=101��MOD=125��VCO����ZComm��˾��V674ME34-LF����ԓ�����£��A��ݔ����RFOUT=1.7452GHz.

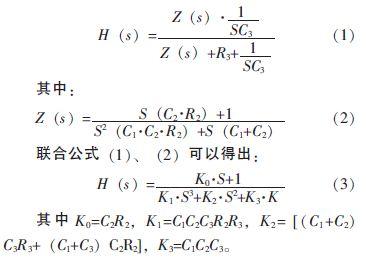

a���O���h·�V����������20kHz����λԣ��50�㣬����λ���ķ�����r��D2��ʾ��

�D2�h·����20kHz�r����λ������D

�ĈD2�п��Ե�֪�����h·�V��������20kHz�r��VCO���������λ��ռ����������λ��оƬ���������λ���t���͛]�ڿ�ݔ����֮�¡��Q��Ԓ�f�����h·�����^խ����20kH������r�£�ᘌ��i��hݔ����̖�M����λ���yԇ����Y�������������ط�ӳоƬݔ������λ����

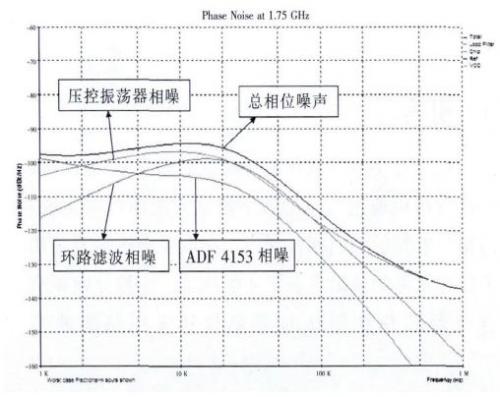

b���O���h·�V����������100kHz����λԣ��50�㣬����λ���ķ�����r��D3��ʾ��

�D3�h·������100kHz�r����λ������D

�ĈD3�п��Ե�֪�����h·�V��������100kHz�r��VCO���ڿ���λ����ؕ�I�@���ؽ��ͣ�оƬ���������λ��ռ����������λ����10kHz�ԃȣ�����λ��ݔ�������������cоƬ���������λ���غϡ��ɴ˿��Ե�֪�����h·�����^������100kHz������r�£�ᘌ��i��hݔ����̖�M����λ���yԇ����Y��������������ӳоƬݔ������λ����

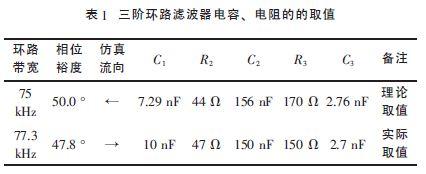

�����о���ADF 4154����Ҫ�yԇ�l�c��1.7452GHz��fPFD=25MHz��RSET=5.1k���������yԇҪ���M�оC�ϵĿ��]���O���˭h·����75kHz����λԣ��50��ļs���l�������M��ADF 4153������·�OӋ�r��������Ҫ�_�J��ʹ�õ�VCO��̖����˷Q���ܡ�Ȼ���ٸ���ADI��˾�ṩ��ADIsim-PLLܛ���M�����A�h·�V�������OӋ����ܛ���ó�C1~C3��R2��R3�ľ��wȡֵ���ٸ����F�еĘ˷Q������ֵ�M���{������������H�OӋ�ĭh·��������λԣ�ȡ����H�������1��ʾ��

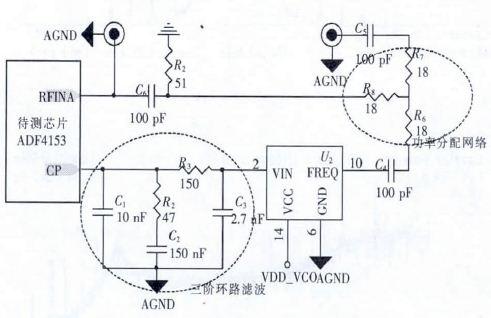

�ɴˣ��҂��_���˭h·�V�����и�����ݡ�����ȡֵ�����OӋ�˿�����ADF 4153оƬ�yԇ���·ԭ��D����D4��ʾ��VCO��ݔ�����H��Ҫ�B���ⲿ�l�V�x�M�Мyԇ��߀��Ҫͨ�^��ݷ�����ADF 4153��REFINA�ˣ�ͬ�rREFINA��߀��Ҫ�A��SMA�^�������lݔ���l�ʷ������`���Ȝyԇ��һ�����ε����W�j�������VCOݔ����̖���ʵ��ٷ��䡣

�D4�h·�V���������l�·�OӋ

3�h·�V�����Ĝyԇ��C

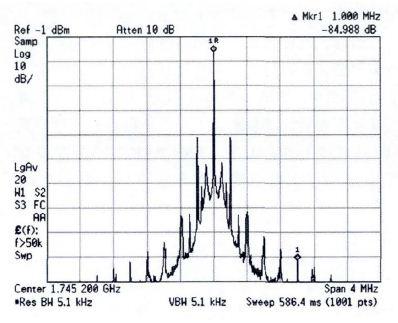

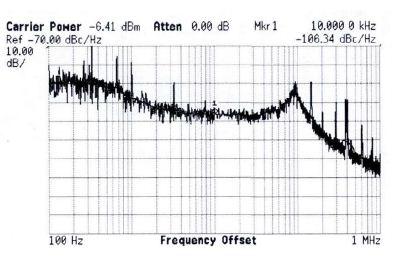

�ڷ���Ļ��A�ϣ��҂��OӋ���ӹ���ADF4153�Ĝyԇ�壬������Ӌ�����ݡ����ֵ�M���˭h·�V���W�j������Agilent8257D���l��̖Դ�ṩ250MHz����fREFIN��ͨ�^SPI�˿��O��fPFD=25MHz��N=69��4/5���lģģʽ��ICP=5mA��FRAC=101��MOD=125.ʹ���l�V�x�y��ݔ����̖���܉������i����1.7452GHz����D5��ʾ���D6��ԓ�l�c����λ���yԇ�D�����y��λ����-106.34dBc/Hz.�h·�����s��85kHz���c��Փֵ77.3kHz����һ���IJ�ࡣ�@�������ڷ���r���]�п��]�yԇ���߾����yԇ�����ȴ��ڵļ�����������µ�ƫ������ں��������ԃȡ�

�D5ݔ����̖�l�V

�D6��λ���yԇ�D

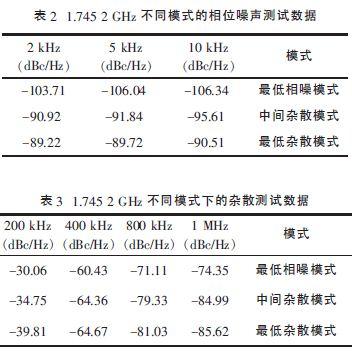

ᘌ�оƬ�M�в�ͬ����ģʽ�µ���λ�����sɢ�M�Мyԇ���yԇ�Y�����2��3��ʾ��

�����փ�Ҏ����͵���λ��ģʽ��5kHz�lƫ����λ��PN��-95dBc/Hz�����yԓ�c��-106.04dBc/Hz���yԇ�Y���M��Ҫ��

�����փ�Ҏ�����g�sɢģʽ��1MHz�lƫ���sɢSN��-65dBc/Hz�����yԓ�c��-84.99dBc/Hz���yԇ�Y���M��Ҫ��

�C��������ԓ�V�������OӋ���_���A�ڵ��OӋĿ�ˣ��M�㲻ͬģʽ�µ��sɢ������yԇ��Ҫ������ADF 4153оƬ�����ܜyԇ��

4�Y���Z

������Ҫ����оƬ�yԇĿ�ģ�ᘌ�����·�еĭh·�V�����OӋ���M��ӑՓ�����нo����һ�N���Ρ����еĹ��̻�Ӌ�㷽�������̣��������M������C�yԇ���yԇ�Y���M��оƬ�yԇ����Ҫ���@�N�����ѽ������ڶ��С�����l�l�ʺϳ����Ĝyԇ�·���OӋ�С�

|