ժҪ

�����}�_푑�(FIR)�͟o���}�_푑�(IIR)�V�������dz��õĔ�����̖̎���㷨---�����m�������l̎�푪�á���ˣ��ڵ��͵����lϵ�y�У�̎�����Ⱥ˵ĺܴ�һ���֕r�g����FIR��IIR�V����������̖̎�����ϵ�Ƭ��FIR��IIRӲ��������Ҳ�քe�Q��FIRA��IIRA���҂����������@ЩӲ�����������֓�FIR��IIR̎���΄գ��Ⱥ�ȥ��������̎���΄ա��ڱ����У��҂���������ͬ��ʹ��ģ���Լ����r�yԇʾ����̽ӑ����ڌ��`�������@Щ��������

����

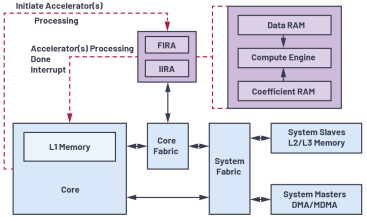

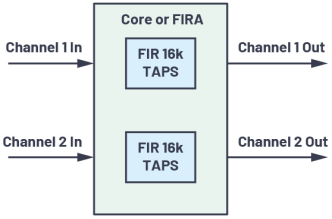

�D1.FIRA��IIRAϵ�y����D

�D1�@ʾ��FIRA��IIRA�ĺ�������D���Լ������c����̎����ϵ�y���YԴ�Ľ�����ʽ��

�� FIRA��IIRAģ�K����Ҫ����һ��Ӌ�����棨���ۼ�(MAC)��Ԫ���Լ�һ��С�ı��ؔ�����ϵ��RAM��

�� u ���_ʼ�M��FIRA/IIRA̎�����Ⱥ�ʹ��ͨ���ض���Ϣ��ʼ��̎�����惦���е�DMA��ݔ���ƉK(TCB)朡�Ȼ��ԓTCB朵���ʼ��ַ����FIRA/IIRA�ָᘼĴ������S������FIRA/IIRA���ƼĴ����Ԇ��Ӽ�����̎����һ������ͨ����������ɣ��͕���Ⱥ˰l��һ���Д࣬�Ա�Ⱥˌ�̎�����ݔ�����ں��m������

�� u ����Փ���v����õķ����nj�����FIR��/��IIR�΄ՏăȺ��D�ƽo�������������S�Ⱥ�ͬ�r�����������������ڌ��`�У��@����ʼ�K���У��e�Ǯ��Ⱥ���Ҫʹ�ü�����ݔ���Mһ��̎�������қ]�������������΄���Ҫͬ�r��ɕr�����@�N��r�£��҂���Ҫ�x����m�ļ�����ʹ��ģ�́��_�����Ч����.

�ڱ����У��҂���ӑՓᘌ���ͬ���È�����������@Щ�������ĸ��Nģ�͡�

���rʹ��FIRA��IIRA

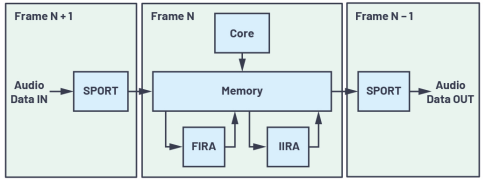

�D2.���͌��r���l������

�D2�@ʾ�˵��͌��rPCM���l�������D��һ�����ֻ�PCM���l����ͨ�^ͬ�����ж˿�(SPORT)���գ���ͨ�^ֱ�Ӵ惦���L��(DMA)�l�����惦�������^�m���Վ�N+1�r����N�ɃȺ˺�/�������̎����֮ǰ̎���Ď�(N-1)��ݔ��ͨ�^SPORT�l����DAC�M�Д�ģ�D�Q��

������ʹ��ģ��

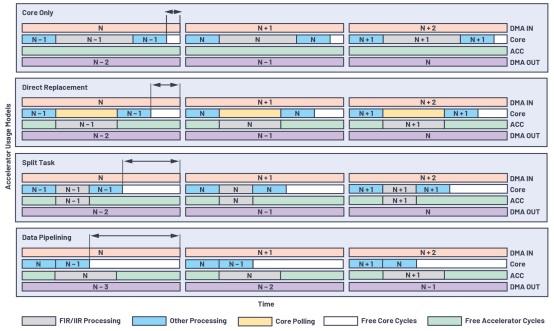

��ǰ�������������õIJ�ͬ��������Ҫ�Բ�ͬ�ķ�ʽʹ�ü�������������ȷ֓�FIR��/��IIR̎���΄գ����M���ܹ�ʡ�Ⱥ����������������������ĸߌӴνǶȁ�����������ʹ��ģ�Ϳɷ֞����ֱ�����������΄պ͔�����ˮ����

ֱ�����

�� �Ⱥ�FIR��/��IIR̎��ֱ�ӱ�������������Ⱥ�ֻ��ȴ���������ɴ��΄ա�

�� ��ģ�̓H�ڼ�������̎���ٶȱȃȺ˿�r����Ч������ʹ��FIRAģ�K��

����΄�

�� FIR��/��IIR̎���΄��ڃȺ˺ͼ�����֮�g���䡣

�� ������ͨ���ɲ���̎��r����ģ���e���á�

�� �������Եĕr����㣬�ڃȺ˺ͼ�����֮�g����ͨ��������ʹ���ߴ����܉�ͬ�r����΄ա�

�� ��D3��ʾ���cֱ�����ģ����ȣ���ʹ��ģ�Ϳɹ�ʡ����ăȺ����ڡ�

������ˮ��

�� �Ⱥ˺ͼ�����֮�g�Ĕ��������M����ˮ��̎����ʹ�����܉��ڲ�ͬ�������ϲ���̎����

�� u ��D3��ʾ���Ⱥ�̎����N������Ȼ�Ӽ�������ԓ���M��̎�����Ⱥ��S���^�m�Mһ������̎������������һ�����Юa���ĵ�N-1����ݔ����ԓ�������S��FIR��/��IIR̎���΄���ȫ�D�ƽo����������ݔ������һЩ���t��

�� u ��ˮ�����Լ�ݔ�����t�����ܕ����ӣ����wȡ�Q������̎����д��FIR��/��IIR̎�����Ĕ�����

�D3�f�������l����������ڲ�ͬ������ʹ��ģ�͵������A��֮�g��ݔ---DMA IN���Ⱥ�/������̎����DMA OUT����߀�@ʾ��ͨ�^���ò�ͬ�ļ�����ʹ��ģ�͌�FIR/IIRȫ����̎���D�Ƶ��������ϣ��c�Hʹ�ÃȺ�ģ����ȣ��Ⱥ˿��e����������ӡ�

�D3.������ʹ��ģ�ͱ��^

SHARC̎�����ϵ�FIRA��IIRA

����ADI SHARC®̎����ϵ��֧��Ƭ��FIRA��IIRA�����f���£���

�� ADSP-214xx (���磬 ADSP-21489)

�� ADSP-SC58x

�� ADSP-SC57x/ADSP-2157x

�� ADSP-2156x

�@Щ̎����ϵ�У�

�� Ӌ���ٶȲ�ͬ

�� ��������ģ�ͱ��ֲ�׃��ADSP-2156x̎�����ϵ��Ԅ�����ģʽ(ACM)���⡣

�� FIRA���Ă�MAC��Ԫ����IIRAֻ��һ��MAC��Ԫ��

ADSP-2156x̎�����ϵ�FIRA/IIRA���M

ADSP-2156x��SHARC̎����ϵ���е����µĮaƷ�����ǵ�һ��κ�1 GHz SHARC̎��������FIRA��IIRAҲ����1 GHz���\�С�ADSP-2156x̎�����ϵ�FIRA��IIRA�c��ǰ��ADSP-SC58x/ADSP-SC57x̎������ȣ����ж�헸��M��

���ܸ��M

�� Ӌ���ٶ������8������SCLK-125 MHz��CCLK-1 GHz����

�� ���ڃȺ˺ͼ������������ÃȺ˽Y�����F�˸��o�ܵļ��ɣ���˜p���˃Ⱥ˺ͼ�����֮�g�Ĕ�����MMR�L�����t��

���ܸ��M

������ACM֧�֣��ԱM���p���M�м�����̎������ăȺ˸��A����ģʽ��Ҫ�������������ԣ�

�� ���S��������ͣ���M�ЄӑB�΄���ꠡ�

�� �oͨ�������ơ�

�� ֧���|�l���ɣ������������|�l�ȴ�������������

�� ��ÿ��ͨ�������x�����Дࡣ

���Y��

�ڱ����У��҂���ӑՓ��ADSP-2156x�u�����ϣ�������ͬ�ļ�����ʹ��ģ�͌�ʩ�ɂ����r��ͨ��FIR/IIR�����ĽY��

����1

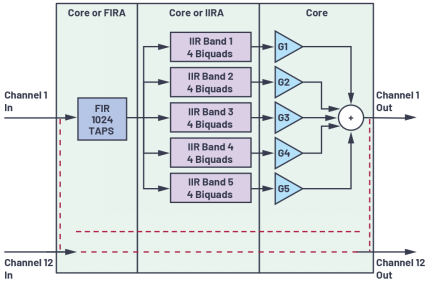

�D4�@ʾ����1�ķ���D���ɘ��ʞ�48 kHz��ģ�K��С��256���ɘ��c������΄�ģ����ʹ�õăȺ��c������ͨ���Ȟ�5:7��

��1�@ʾ�y�õăȺ˺�FIRA MIPS�������Լ��c�Hʹ�ÃȺ�ģ����ȫ@�õĹ��s�Ⱥ�MIPS�Y��������߀�@ʾ������ʹ��ģ�����ӵ��~��ݔ�����t�������҂��������ģ�ʹ�ü�������ϔ�����ˮ��ʹ��ģ�ͣ��ɹ��s���_335�Ⱥ�MIPS��������1�K(5.33 ms)��ݔ�����t��ֱ������Ͳ���΄�ʹ��ģ��Ҳ�քe�ɹ��s98 MIPS��189 MIPS������δ�����κ��~���ݔ�����t��

�D4.����1����D

|

��1.����1�ăȺ˺�FIR/IIRA MIPS���Y

|

|

ʹ��ģ��

|

�Ⱥ� MIPS

|

FIRA MIPS

|

IIRA MIPS

|

���s�Ⱥ�MIPS

|

ʹ��ģ�����t(ms)

|

|

�Hʹ�ÃȺ�

|

337

|

|

|

|

0

|

|

ֱ�����

|

239

|

162

|

75

|

98

|

0

|

|

����΄�

|

148

|

96

|

44

|

189

|

0

|

|

������ˮ��

|

2

|

161

|

75

|

335

|

5.33 (1��)

|

����2

�D5�@ʾ����2�ķ���D���ɘ��ʞ�48 kHz��ģ�K��С��128���ɘ��c������΄�ģ����ʹ�õăȺ��c������ͨ���Ȟ�1:1��

�c��1һ�ӣ���2Ҳ�@ʾ�˴������ĽY���������҂��������ģ�ʹ�ü�������ϔ�����ˮ��ʹ��ģ�ͣ��ɹ��s���_490�Ⱥ�MIPS��������1ģ�K(2.67 ms)��ݔ�����t������΄�ʹ��ģ�Ϳɹ��s234�Ⱥ�MIPS�����]�Ќ����κ��~��ݔ�����t��Ոע�⣬�c����1�в�ͬ��������2�ЃȺ�ʹ���l���پ��e��̎�������Ǖr��̎�����@���Ǟ��̎��һ��ͨ������ăȺ�MIPS��FIRA MIPS�ٵ�ԭ���@�Ɍ���ֱ�����ʹ��ģ�͌��Fؓ�ăȺ�MIPS���s��

�D5.����2����D

|

��2.����2�ăȺ˺�FIR/IIRA MIPS���Y

|

|

ʹ��ģ��

|

�Ⱥ�MIPS

|

FIRA MIPS

|

���s�Ⱥ�MIPS

|

ʹ��ģ�����t(ms)

|

|

�Hʹ�ÃȺ�

|

493

|

|

|

0

|

|

ֱ�����

|

515

|

511

|

�C22

|

0

|

|

����΄�

|

259

|

257

|

234

|

0

|

|

������ˮ��

|

3

|

511

|

490

|

2.67 (1��)

|

�YՓ

�ڱ����У��҂�����������ò�ͬ�ļ�����ʹ��ģ�͌��F�����MIPS��̎��Ŀ�ˣ��Ķ��������Ⱥ�MIPS�D�Ƶ�ADSP-2156x̎�����ϵ�FIRA��IIRA�������� |