����Ħ���_�����F�� �w˼������ ����ʹ�õ��^�r�� SAA1042 ���M늙C���� IC�����OӋ���������˻��� CPLD���͔��ɾ���߉�������IJ��M늙C�������F��ԓ����Ҳ����ȡ������ SAA1027 �� UCN5804B ���OӋ�е�������ԓ�OӋ�Hʹ���������Ԫ ِ�`˼ XC9536 CPLD����˿�����һ��С����CPLD�Ќ��F�������M늙C������CPLD���M늙C������Ҫ�r犡������L�͏�λݔ�롣�r�ݔ�����߉�ƽ�}�_�������}�_����߅���ϼ��

����� CW/CCW��형r�/��rᘣ�ݔ��Q����늙C�����D������늙C��늚��B�ӣ�����ݔ�뱣���� 0V ͨ���a�� CW ���D��߉ 1 ݔ��a�� CCW ���D�����L����ȫ����벽��ݔ��Q����늙C��ÿ���r��}�_�µĽǶ����D������ԓݔ�����ƽ����늙Cᘌ�ÿ��ʩ�ӵĕr��}�_����һ�������IJ��M����ݔ��a���벽����λݔ���ϵĸ��ƽʹ늙C̎����ǰ���x�Ġ�B��������CPLD�����κ�ݔ��r��}�_��

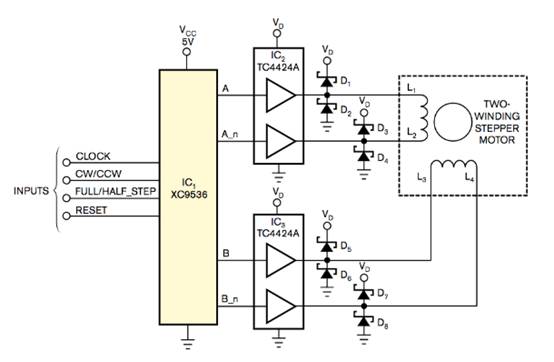

CPLD��ݔ������A���A_n���Լ�B���B_n�࣬ÿ����λͨ�^�ⲿ�Դ����IC����늙C�ăɂ���Ȧ֮һ2 �ͼ����·3 ����늙C�Ę˷Q늉����D1 ).ÿ������ݔ���˵�һ��Ф�ػ����O����ͨ�^���D�@�M�������ĸ���늉�˲׃���g���o������ݔ������ MOSFET �����c�Ȳ����O�����ʹ�ã����� оƬ�� TC4424A �p��������ʡȥ���ⲿ���O�ܵ�Ҫ��

�D1 ���挣�ò��M늙C���������ɾ���߉������IC1 �������M늙C��̖ʩ�ӵ�늙C����IC2 �ͼ����·3 .

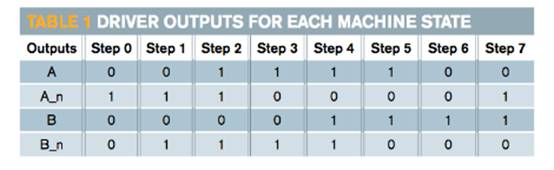

CPLD�ij������һ���ˑBĦ�����ޠ�B�C��������늙C�İ˂��벽�B�� ��1 �@ʾÿ��Ӌ��C��B���ӳ���ݔ������ȫ����Bģʽ�£���B�C�H���в��E 0�����E 2�����E 4 �Ͳ��E 6����ÿ���r��}�_�������أ���� CW/CCW ����ƽ���t�C����B�IJ��M ��n�� ׃�鲽�M ��n+1������� CW/CCW ����ƽ���t�IJ��M ��n�� ׃�鲽�M ��n�C1����������һ�� ͨ�� VHDL ���F ���M늙C�����̼����mȻԓ���a�Ǟ�XC9536 CPLD�����ģ�����Ҳ�m�����κ�CPLD��FPGAĿ�������� |