����1��DCDC��Դ����

����DCDC������Ӱ�����������Ҫ��

����

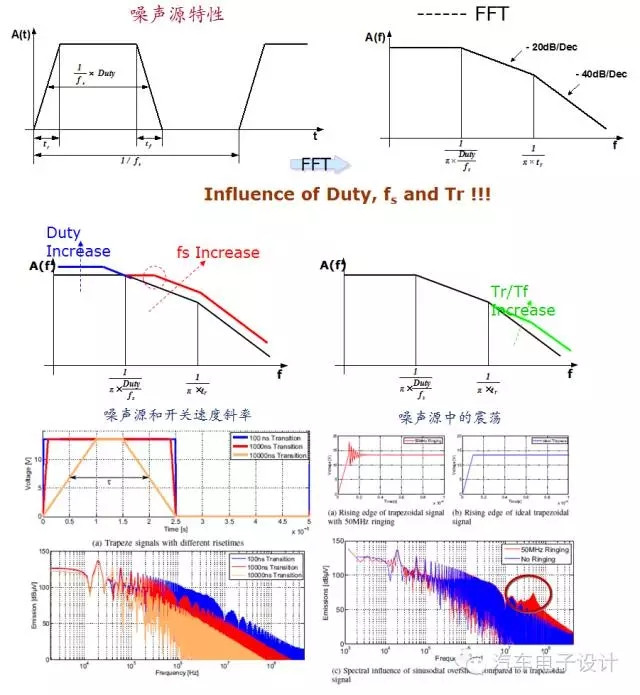

����ռ�ձ�Duty��ռ�ձ�������������������

�����_�P�l��Fs���ǵ���˥�p׃���l�V�������ˣ��_�P�l��һ���҂����Է֞�ׂ����

����20��100Khz��늸��^������ijɱ����ߴ�������l�OӋ��������һ�N�x��

����100��550Khz����Ҫ���x���x��

�����_�P�l����Ҫ��늸д�С��Ч�ʡ�RE/CE������Ӱ푱��^��

���������r�gTr

������ע���_�P�l�ʵ�Ӱ��䌍�ܴ��H�H��EMC��Ч�����ڲ�ͬ�İ���������Եõ���ͬ��Ӱ��Pϵ���硶Choosing the optimum switching frequency of your DC/DC converter����ʾ��

����

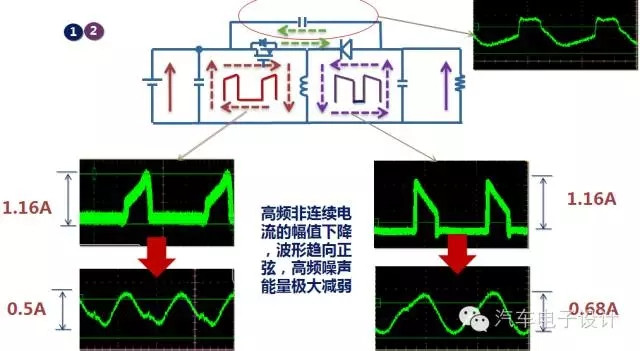

����2��������İ�����ʾ

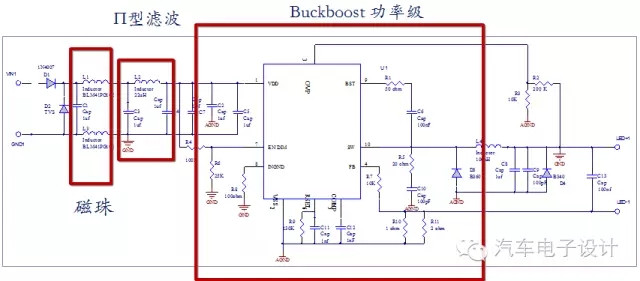

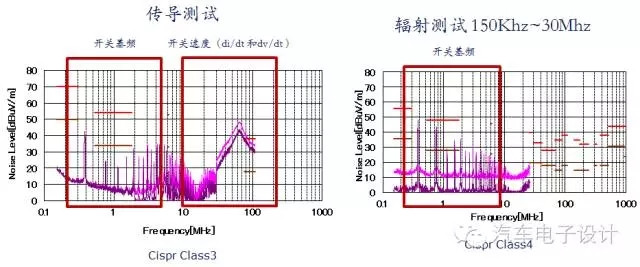

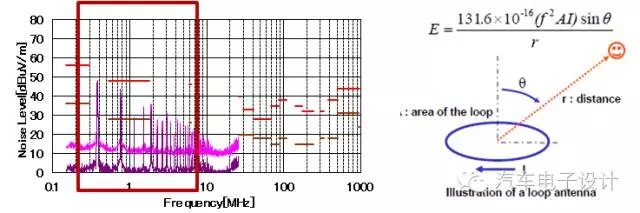

����2.1���@��һ�����͵�BuckBoost���Դ�·���]�в�����Ҫ�^CISPR25 Class 3

����

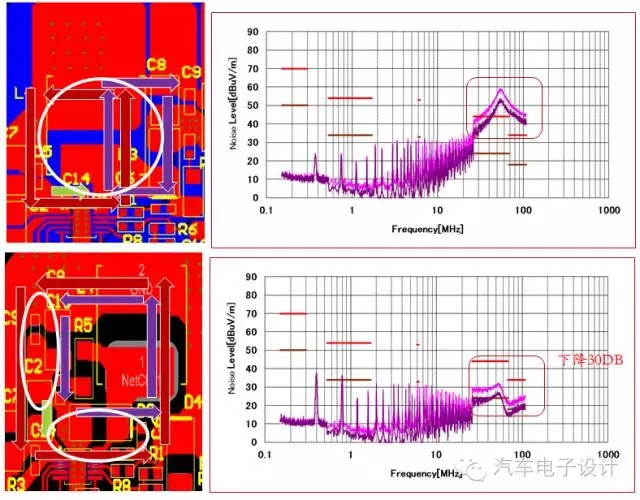

����2.2 ���y�Y��

����

����2.3 ���Ĵ�ʩ

����2.3.1 ԭ������

����

�����ɂ��_�P�h·�к��з��B�m�Ĵ�����h·������Ҫ����Դ

��������Vin��Vss��ݿ��Ԝp�ٸ��l�h·�����

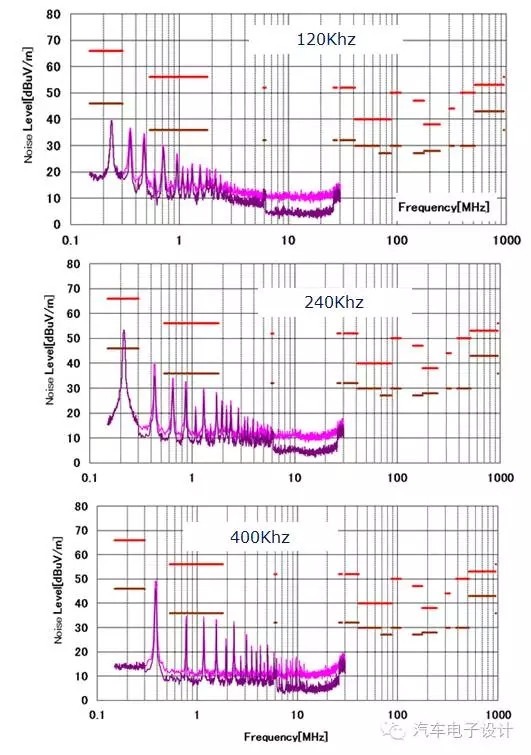

����2.3.2 �l���x��

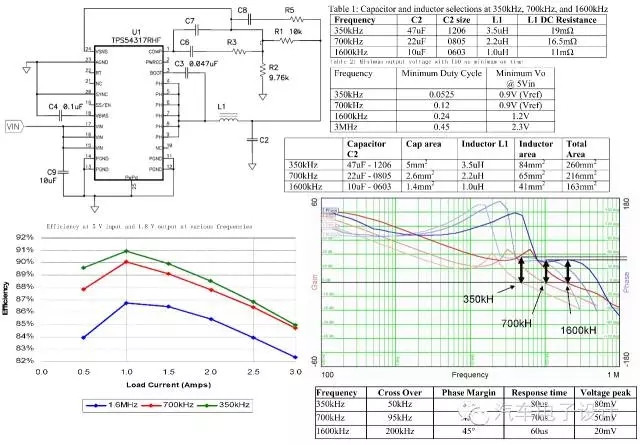

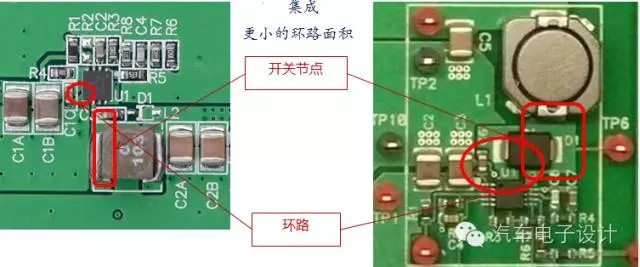

�����������������С���h·��e���l�ʳ����ȣ��;��x�ɷ���

����

�����������Ξ鲻ͬ�l�ʵ�Ч�����ȣ�120��240��400Khz��������ɫ�鶶�l��Ч��

����

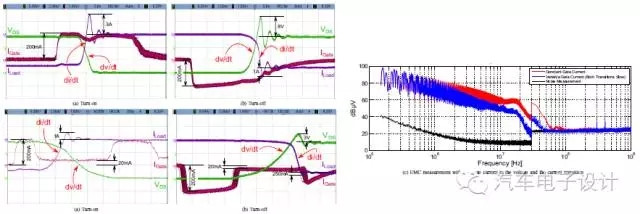

����2.3.2 �_�P�ٶȵă���

����

����2.3.3 ���փ���Ӱ�

�����ڲ����ϱM���܌�C14��Vin-Vss��ݣ������m�����O�ܺ�MOSFET߅�Ϝp�ٸ��l�h·��e

����

���������nj�����Ƭ

����

�����a��һЩ���P�IJ��ϣ����_оƬ�S�ҵ�Ŭ�����҂��ܼ�����OӋ�ֶ���Ҫ������

����1��ݔ��V������

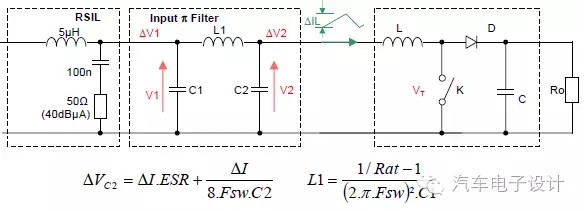

����RSIL filter 5��H 100nF 50��

����

����2��ݔ���V������

����

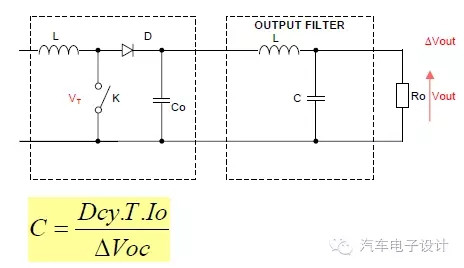

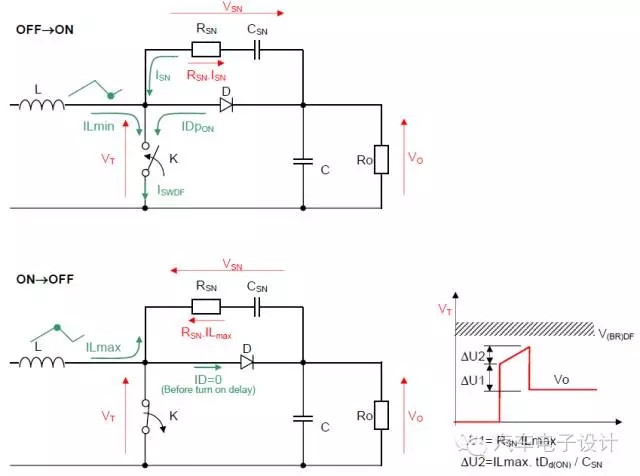

����3��Snubber�·

����

�����Y��

����1�����x�����ֵİ������Y���҂����Զ����Ͷ��ԵĿ��@Щ�������x���Hԇ�ĽY��

����2���@�����OӋ����Ҫ��ͨԭ����Ӌ�㡢����ԇ�͌��H��C�ĭh·